2PFLOPS超えのGPGPUを開発した、中国新興企業:チップレットを適用(1/2 ページ)

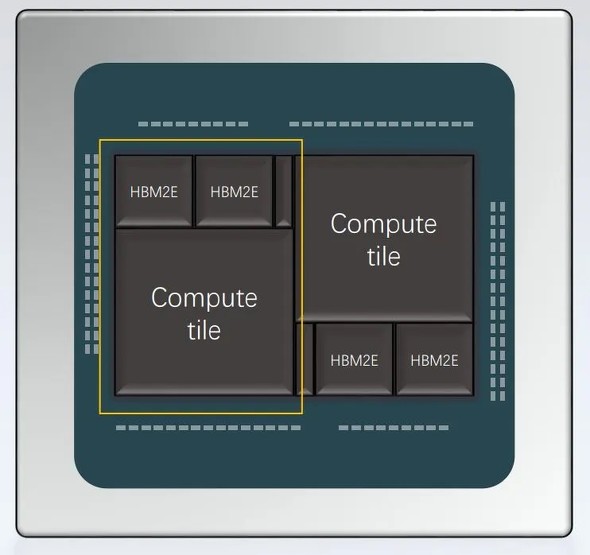

2022年8月21〜23日にオンラインで開催された「Hot Chips」において、中国の新興企業Biren Technology(以下、Biren)がステルスモード(製品や開発の中身を明らかにしないこと)を脱し、データセンターにおけるAI(人工知能)学習と推論向けの大型汎用GPU(GPGPU)チップの詳細を明らかにした。同社の「BR100」は、TSMCの7nmプロセス技術に基づく537mm2のチップレット2つで構成されている他、CoWoS(Chip on Wafer on Substrate)パッケージに4つのHBM2eを積層している。

チップレット構成でコスト削減&高性能化

2022年8月21〜23日にオンラインで開催された「Hot Chips」において、中国の新興企業Biren Technology(以下、Biren)がステルスモード(製品や開発の中身を明らかにしないこと)を脱し、データセンターにおけるAI(人工知能)学習と推論向けの大型汎用GPU(GPGPU)チップの詳細を明らかにした。同社の「BR100」は、TSMCの7nmプロセス技術に基づく537mm2のチップレット2つで構成されている他、CoWoS(Chip on Wafer on Substrate)パッケージに4つのHBM2eを積層している。

BirenのCEO(最高経営責任者)であるLingjie Xu氏は「われわれはより大きなチップを構築すると決めていて、BR100の設計を経済的に実行可能なものにするためパッケージングに工夫が必要だった。BR100のコストは、ワット当たりの性能や平方ミリメートル当たりの性能という観点で、より優れたアーキテクチャの効率によって計ることができる」と述べた。

BR100はINT8で2PFLOPS、BF16(BFloat16)で1PFLOPS、あるいはFP32で256TFLOPSの演算性能を実現する。さらにBirenの新しい演算フォーマット「TF32+」では演算性能は512TFLOPSまで高まる。このGPUは16ならびに32ビットフォーマットもサポートするが、64ビットには対応していない(科学計算を除き、64ビットはAIの作業負荷に幅広く用いられていない)

チップレットを用いた設計であるということは、Birenがレチクルの制限を打ち破りながら、ダイの小型化によってコストを削減できるという優位性を生み出したことを意味する。Xu氏によると、同じGPUアーキテクチャをベースとした仮想レチクルサイズの設計と比べると、2つのチップレットで構成されたBR100は性能が30%高まり(コンピュートダイの面積が25%大きくなった)、歩留まりは20%向上したという。

チップレット設計の他のメリットとして、同じテープアウトで複数の製品を作ることができる点がある。Birenのロードマップには、単一チップレットを備える「BR104」も含まれている。

BR100はOCPアクセラレータモジュール(OAM)フォーマットで提供される。一方、BR104はPCIeカードに対応するようになる。Xu氏は、BR100のOAMモジュールを8つ組み合わせれば、「AI専用としては、世界で最もパワフルなGPGPUサーバができる」と述べた。BirenはOEM/ODMメーカーとも連携している。

Copyright © ITmedia, Inc. All Rights Reserved.