CXL/UCIeから考える光インターコネクト技術:光伝送技術を知る(22) 光伝送技術の新しい潮流と動向(3)(1/4 ページ)

「ChatGPT」などのAI技術に後押しされ、データセンターは拡張の一途をたどるとされている。その際、光技術はどうあるべきなのか。今回は、チップレット間のインターコネクト技術である「CXL」や「UCIe」に着目し、ここから求められるであろう光インターコネクトの姿を探る。

「ChatGPT」がきっかけとなってAI(人工知能)が世の中を騒がしている。AIがさまざまな分野で革新のエンジンとなることは予測されていたが、ChatGPTがそれを加速した。これに伴い、次世代データセンタにおいて膨大なパラメーターを有するAI/ML(Machine Learning)をサポートする大規模計算システム(Massive Node Compute System)が実現されると考えている。新しいシステムは経済的(Total Cost of Ownership[TCO]の低減)で、多様なユーザーやアプリケーションに対応できなければならない。

AI/MLは、汎用チップよりも、専用チップによる計算システムが効率的、経済的であるとされる。そして、AIモデルや学習アルゴリズムなどにより使用チップ数やメモリ/ストレージ量が大幅に異なるためDisaggregated Systemが適している。ICの集積度や、AIモデル、アルゴリズムは引き続き進化するので、数年に一度のチップ交換も容易でなければならない。

また、前回述べたように、毎年2倍のNode(チップ)数の増加が期待されているため、このNode数のスケールアウトも可能にしなければならない。このスケールアウトでは、従来のサーバを中心としたHyper-Scale Data Centerとは異なり、Networkも増殖していく必要がある。

2025年には数万あるいは10万以上のNodeがつながったコンピュートシステムが想定されるがそれはスーパーコンピュータと同じ規模であり、スーパーコンピュータとの融合も視野にある[1]。

[1]Daniel Reed, et al, arXiv:2203.02544

さらに、2000年代にはデナード則が崩壊し、2010年代には「ムーアの法則」が飽和したといわれた。これからは、微細化とともにトランジスタ当たりの価格が飽和あるいは上昇していくと予測される。この領域では、ムーアの法則の恩恵を受けてきたSoC(System on Chip)に代わる技術として、チップの機能や規模を最適に分割し、それぞれに適したプロセスで製造されたチップを1パッケージに収めたチップレット/SiP(System in Package)が期待され、研究開発が進んでいる。

これらを背景にして、光技術はどうあるべきだろうか。今回は、Disaggregated Compute Systemに触れ、それを実現すると考えられている「Compute Express Link(CXL)」と、チップレット/SiPのインタフェースとなる「Universal Chiplet Interface Express(UCIe)」の標準規格に注目する。さらに、ここから求められるであろう光インターコネクトの姿を考えてみたい。

Composable Disaggregated Compute System

最近のLightwaveのWebキャスト[2]で、NVIDIAのLarry Dennisonが述べたようにMassive Nodeを実現するには2つのスケールアウトを考えなければならない。

[2] “Disaggregation and Optical Interconnect in AIHPC Networks,” Lightwave Webcast, June 2023

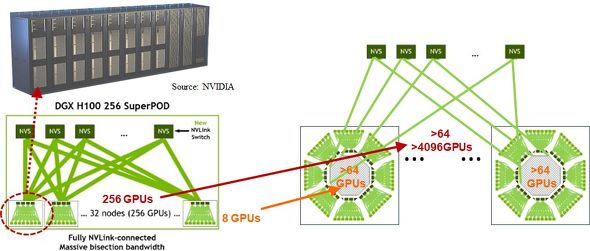

NVIDIAの“SuperPOD”と呼ばれる最新システムは、8個の「H100」GPUと30TバイトのNVMe SSDを搭載した“DGX”シャシーをラックに4個並べ、そのラックを8個並べて設置した256個のGPUで構成される。図1に示すように、方向性の一つは、広帯域ネットワークで結合されたDGX内の8個のGPU数を、64個などにスケールアウトさせることである。AIの推論(Inference)に有効だという。

もう一つの方向性は、中帯域のDGX間ネットワークで結合された合計256個のGPU数を、例えば数千の規模にスケールアウトすることだ。学習(Training/Machine Learning)に有効だという。また、忘れてならないのは、大容量のストレージやメモリであり、このスケールアウトも考えなくてはならない。

このようなスケールアウトに伴って起こるのが、効率そして経済性の問題である。

「AIモデルによって、学習や推論に必要なGPUの個数やメモリの容量が大きく異なる」という問題が指摘されている(GPU数は少ないが大容量のメモリが必要、あるいはその逆もある)。大規模システムでは、各エレメントの待機時間を最小にする工夫が必須だ。このため、多くのプログラムを走らせ、無駄に待っているGPUやメモリを極力減らすことが重要になる。

この実現に向け推進されているのが、本連載でも以前から述べているDisaggregated Compute Systemである。基本は“Pool and Composite”であり、「Composable Disaggregated System」ともいう。xPU(CPU、GPU、NPU、TPUなど)やメモリといったリソースをPoolし、必要な数量をCompositeして計算させる。リソースに対する要求の異なる仕事(ワークロード)をどう効率よく実行していくかを管理するソフトウェアが重要であるが、必要なリソースを接続するネットワークもキーとなる。

Copyright © ITmedia, Inc. All Rights Reserved.