チップレット戦略 Armはどう攻めるのか:パートナーシップを次々と発表(1/2 ページ)

注目が高まるチップレットにおいて、Armはどのような戦略を持っているのか。Armのパートナーシップを振り返りながら検証してみたい。

Armは現在、高度に集積された大規模シリコンに向けたソリューションであるチップレットの設計や開発に関して、どのような計画を立てているのだろうか。Armは、現在の半導体分野において最もエキサイティングなチャンスの一つであるチップレットの設計図を、徐々に明らかにしている。

Armにとって重要なのは、CPUチップレットか、カスタマイズされたアプリケーション特化型のチップレットかどうかに関係なく、マルチダイシリコンプラットフォームにおける同社の計算ビルディングブロックの位置付けを確保することだ。このため同社は、Armベースのシステムが“チップレット革命”における不可欠な要素になるよう、半導体設計メーカーや、半導体IP(Intellectual Property)サプライヤー各社との間で戦略的パートナーシップを締結している。

Armは、チップレット設計のための共通設計フレームワークを定義する、標準化の取り組みにも積極的に関与している。ArmのAMBA(Advanced Microcontroller Bus Architecture)仕様は、過去20年間にわたりSoC(System on Chip)コネクティビティ設計の基盤を形成してきたため、これは非常に重要なことである。

Alphawaveとの協業から読み取れること

Armが、チップレットIPサプライヤーであるAlphawave Semiと協業したことから、Armのマルチダイシリコンデバイスに関するより大きな計画について、いくつか手掛かりを得ることができるだろう。Alphawave Semiは2023年10月に、Arm Neoverse Compute Subsystems(CSS)をベースとしたチップレットソリューションを開発するためのイニシアチブ「Arm Total Design」に参加している。

Alphawave Semiは、Arm Neoverse CSSコンピュートと、同社のUniversal Chiplet Express(UCIe)対応カスタムシリコンおよび事前構築済みのコネクティビティチップレットを統合する。このため同社のUCIe IPは、Advanced eXtensible Interface(AXI)やCoherent Hub Interface(CHI)などのArmのファブリックインタフェースをサポートし、CXLやHBMx、DDRx、イーサネットなどのインタフェースのコネクティビティを、ArmベースのカスタムSoC/チップレットに簡単に統合することができる。

つまり、Alphawave Semiは、同社の高速コネクティビティIPとチップレットプラットフォームを、Arm Neoverse CSSリファレンスIPソリューションと組み合わせることになる。さらに、同社の専門チームは、3nm/2nm世代のチップレット製造までの微細化を実現する主要なプロセスノードにおいて、Neoverseコアの性能/電力/面積(PPA:Performance, Power, and Area)を強化および最適化していく。

さらに、Alphawave Semiは2024年6月に、AI(人工知能)/ML(機械学習)や、HPC(高性能コンピューティング)、データセンター、5G/6G(第5世代/6世代移動通信)ネットワークインフラアプリケーションなどに向けてArm Neoverse CSSプラットフォーム上に構築した、高度なコンピュートチップレットを開発したと発表している。同社はこのタイアップにより、I/O拡張チップレットやメモリチップレット、コンピュートチップレットなどを含む自社の設計プラットフォームに、重要な差別化要因を追加することになった。

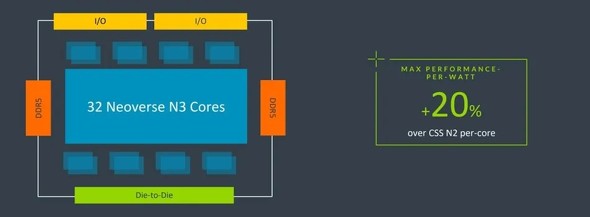

またArmは、日本の設計メーカーであるソシオネクストとのパートナー提携により、TSMCの2nmプロセスノードで32コアCPUチップレットを開発した。このCPUチップレットは、Arm Neoverse CSSプラットフォームを中心として構築され、単一パッケージ内で単一または複数のインスタンス化を実現できるよう設計されている。また、さまざまなアプリケーション向けに性能を最適化すべく、I/Oやアプリケーションに特化したカスタムチップレットも搭載している。

Copyright © ITmedia, Inc. All Rights Reserved.