「超垂直な」メモリホールを高速加工 1000層NANDの実現に向け:Lam Researchの第3世代「Cryo」(2/2 ページ)

Lam Researchは、1000層を超える3D(3次元) NANDフラッシュメモリの加工に向け、極低温絶縁膜エッチング技術の最新世代「Cryo 3.0」を発表した。100:1という高いアスペクト比のメモリホールを、極めて垂直に高速で加工できるという。

ΔCDは9nm 垂直な穴を高速に加工

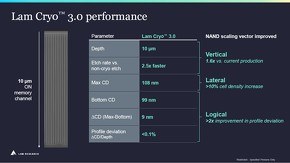

新たにリリースしたCryo 3.0では、最大10μmの深さで加工できることに加え、エッチング速度は常温プロセスに比べて2.5倍になる。メモリホール最上部のCDが108nm、最下部のCDは99nmで、両者の差(ΔCD)は9nmと極めて小さいことも特徴だ。常温プロセス適用時では、ΔCDは30nm程度だという。つまり、アスペクト比が高い穴を“真っすぐに”加工できるということだ。「Cryo 3.0ではアスペクト比100:1の穴を、極めて垂直かつ高速に加工できるようになる」(西澤氏)

左=「Cryo 3.0」の主な特徴/右=Cryoで加工した場合のProfile deviation(ΔCDをメモリホール深さで割った値)の比較。Cryo 3.0は従来世代に比べて、垂直に加工できるようになっている[クリックで拡大] 出所:Lam Research

左=「Cryo 3.0」の主な特徴/右=Cryoで加工した場合のProfile deviation(ΔCDをメモリホール深さで割った値)の比較。Cryo 3.0は従来世代に比べて、垂直に加工できるようになっている[クリックで拡大] 出所:Lam Researchさらに、Cryo 3.0では新しい成分のエッチングガスを採用したことで、従来の常温エッチングプロセスと比較してウエハー1枚当たりの電力消費量を40%削減し、CO2排出量も最大90%削減するという。

Cryo 3.0に対応するチャンバーとして「Vantex Cシリーズ」をリリース済みだ。Cryo 1.0に対応する「Flex Hシリーズ」やCryo 2.0に対応する「Vantex Bシリーズ」など既存のチャンバーにもCryo 3.0を適用できる。

現在、Cryo 3.0は量産に向けた技術評価を行っている段階だ。「ビットコストを下げる手段には複数存在するが、高アスペクト比の穴をいかに垂直に加工できるかという点は、ビットコスト低減において最も象徴的な技術の一つではないか」(西澤氏)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

半導体製造装置でも躍進する中国 日本はシェア低下を止められるのか

半導体製造装置でも躍進する中国 日本はシェア低下を止められるのか

半導体製造の前工程において、日本の半導体製造装置メーカーのシェア低下が止まらない。代わって躍進しているのが中国メーカーである。今回は、半導体製造装置のシェアの推移を分析し、中国勢が成長する背景を探る。 Rapidusの顧客は十分にいるのか 米アナリストの見解

Rapidusの顧客は十分にいるのか 米アナリストの見解

RapidusのCEO(最高経営責任者)である小池淳義氏は、米国EE Timesのインタビューに応じ、2025年4月に2nm世代半導体製造のパイロットラインを稼働予定であると語った。Rapidusを訪問したアナリストによると、TSMCとSamsung Electronicsの新たな競合となるRapidusには、この先まだ大きな障壁が立ちはだかっているという。 Intelの先端パッケージング技術「EMIB」を支援するEDAツール

Intelの先端パッケージング技術「EMIB」を支援するEDAツール

Intelのパッケージング技術「Embedded Multi-Die Interconnect Bridge(EMIB)」は、異種統合マルチチップ/マルチチップレットアーキテクチャの複雑化に対処することを目的とした技術だ。EDAツール大手各社が同技術向けのツールを発表している。 CO2レーザーで高速ビア加工 ガラス複合材基板

CO2レーザーで高速ビア加工 ガラス複合材基板

日本電気硝子が「JPCA Show 2024」で、開発中のガラスセラミックスコア基板を展示した。次世代半導体パッケージコア基板としての用途を想定している。従来の樹脂コア基板と同じように、CO2レーザーで微細貫通穴(ビア)を加工できることが最大の特徴だ。 線幅サブミクロンも視野に パッケージ向け露光装置でウシオとAppliedが協業

線幅サブミクロンも視野に パッケージ向け露光装置でウシオとAppliedが協業

ウシオ電機とApplied Materialsは2023年12月、戦略的パートナーシップの締結を発表した。両社が「DLT(Digital Lithography Technology)」と呼ぶ、半導体パッケージ基板向けの新しいダイレクト露光装置を早期に市場に投入し、大型化や配線の微細化など半導体パッケージ基板への要求に応えることを目指す。