エッジAIにこそ先進パッケージング技術が必要:UMCが解説(1/3 ページ)

クラウドAI向けでよく語られる3次元実装だが、UCMの担当者は先進パッケージングはエッジAIにこそ向いていると語る。

AIがクラウドからエッジデバイスへと急速に移行していることを受け、エッジAIが爆発的な成長を遂げている。エッジAIデバイスは現在、自動車やPC、ロボティクス、スマートフォン、監視などの分野での導入が加速しており、その数は2030年までに年平均成長率(CAGR)17%で伸び、20億台を超えると予測されている。

クラウドAIシステムは、最大1万TOPSの演算能力を提供し、膨大な電力バジェットと多額の投資を必要とするが、エッジAIアプリケーション向けIC設計はそれとはまったく異なる。エッジAIデバイスに必要な電力は通常、わずか1〜50TOPS程度で、厳しい電力制限(0.01〜1W)やコストの制約(10〜1000米ドル)がある。このため半導体メーカーは、帯域幅や性能、フォームファクター、熱的課題、コストの課題などに同時に対応しなければならない。

2次元から3次元実装へ

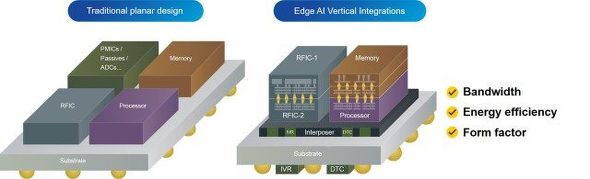

既存のプレーナ型の半導体アーキテクチャは現在、マルチモーダルAIアプリケーションに必要な帯域幅や計算リソースが増加し、チップ面積や消費電力量が増大していることから、限界に達しつつある。業界ではこのような問題に対応すべく、3次元(3D)垂直積層を採用し、プロセッサやメモリ、その他のモジュールなどをインターポーザー上で1つのパッケージ内に統合する動きが進んでいる。

垂直積層のアプローチでは、インターコネクトが短くなるため、信号損失/レイテンシの低減や、電力使用量の削減、デバイスの小型化などが可能になる。また、垂直積層のモジュラー設計により、歩留まりやコスト管理なども向上する。

3D実装は万能ではない

ここで注記すべき重要な点は、垂直積層は万能ではないということだ。イメージプロセッサやパワーマネジメントIC(PMIC)のような一部のモジュールは現在も、プレーナ型設計によって熱ストレスを緩和するというメリットを享受する場合がある。その他のNPU(Neural Processing Unit)やメモリなどは、3Dスタッキングで大幅な性能向上を実現できる。「最も大きなメリットを得られる部分に積層する」という選択的な垂直統合が、半導体設計メーカーのエッジAIに対するアプローチの仕方を形作っている。

Copyright © ITmedia, Inc. All Rights Reserved.