不揮発メモリ新時代(後編):メモリ/ストレージ技術(2/5 ページ)

現在のDRAMやNAND型フラッシュメモリの用途に向けた次世代不揮発メモリの候補は4種類ある。FeRAM、MRAM、PRAM、ReRAMだ。ただし、どれか1つの不揮発メモリで全用途に対応することは難しそうだ。これはどの不揮発メモリにも何らかの欠点が存在するからだ。後編では不揮発メモリの用途や各不揮発メモリの性能向上策、技術動向について解説する。

SSDへの採用やNOR型の置換から

エルピーダメモリは、携帯電話機やデジタルカメラなど携帯型機器に現在採用されているモバイルDRAMをPRAMで置き換えようとしている。

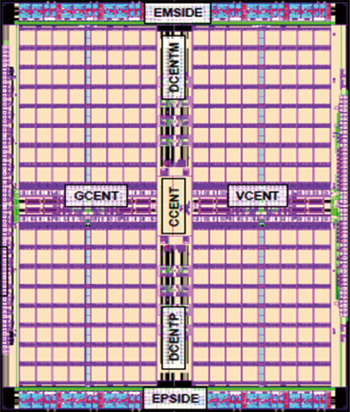

容量が128Mビットの品種を開発中だ。供給電圧やアクセスタイミングなどは全てモバイルDRAMと同じ仕様とした。120nmの製造技術を用いた品種の試作を経て、2008年9月には70nm品を開発した(図3)。「現在は信号比が数十倍あり、120nm品に比べて70nm品ではばらつきがかなり低減した」(エルピーダメモリの取締役執行役員でCTOを務める安達隆郎氏)。2009年中には65nm以下の製造技術を用いた、より容量の大きな品種を開発する予定である。

PRAMの問題点は、書き換え回数に制限があることだ。素子の内部に電流を流し、結晶構造自体を変化させるため、書き換えを繰り返すと信号比が次第に小さくなってメモリとして機能しなくなる。書き換え可能回数は1012回で、不揮発メモリとしてMRAMに次いで多いが、「回数の大小ではなく、書き換え可能な回数に制限があること自体、DRAMの顧客がまだ納得しない。開発を続けているが、1012回を超える書き換え回数が実現できておらず、現時点では顧客にDRAMの完全な代替品として採用してもらうことは難しい」(同氏)。

PRAMはDRAMとNAND型フラッシュメモリのいわば中間の性質を持つ。そのため、現在のNAND型フラッシュメモリにはビット当たりの製造コストでかなわず、DRAMには現時点で書き換え回数が追い付かない中途半端なメモリともいえる。このため、「PRAMの用途はいったん見えにくくなっていた。しかし、2008年に急成長したSSDがPRAMの用途として突破口になり得る」(同氏)という。現在のSSDでは書き込み速度を高めるためにDRAMを組み合わせた品種があるが、PRAMを使えば単独で装置を構成しても高速に動作し、さらに現在のSSDの書き換え回数制限(106回)をはるかに上回るからだ。DRAMの置き換えを目指しつつも、まずはSSDで市場を築くという戦略だ。

一方、ニューモニクス・ジャパンが考えるように、PRAMで既存のNOR型フラッシュメモリを置き換える、もしくはNOR型フラッシュ・メモリの高性能版として用いる場合は、書き換え回数の制限は問題にならない。NOR型フラッシュメモリ自体の書き換え可能回数は106回で、PRAMに比べて少ないからだ。コスト面でもPRAMへの移行に無理が少ない。「NOR型フラッシュメモリはDRAMと一緒に使われている。DRAMの用途のうち、比較的高速な書き込みが必要な部分はそのまま残るが、そうでない部分はPRAMに置き換えられる。つまりNOR型フラッシュメモリと大量のDRAMの組み合わせが、PRAMと少量のDRAMの組み合わせに置き換わる。PRAMの製造コストはNOR型フラッシュメモリよりも高いが、システム全体のDRAMの容量が少なくて済むため、全体の部品コストはNOR型フラッシュメモリを採用した場合と同程度にもっていけるだろう」(同社で技術部部長を務める桑原弘幸氏)とする。

同社は既に90nmの製造技術を用いて、NOR型フラッシュメモリ・チップと端子互換性を備えた容量128MビットのPRAMチップのサンプル品を提供しており、今後、より微細な製造技術を適用した大容量品を製造していく。例えば、同社はモバイルDRAMインタフェースを備えた1GビットのNOR型フラッシュメモリ「Velocity LP NV-RAM」の量産を2008年7月に開始した。これは携帯電話機などに向けた製品だ。同社のロードマップによれば、Velocityの上位品種にPRAMを適用するという。

韓国Sumsung Electronicsは大容量のPRAMチップを早くから試作しており、2006年9月に512Mビット品の開発完了を発表した。当初はNOR型フラッシュメモリの置き換えを狙っており、2008年に製品化するとしていた。技術開発は継続しているものの現時点では製品計画を明らかにしていない*1)。

*1) 2006年の時点でセル面積は5.8F2と小さい。同社は2008年12月に米国で開催された半導体素子の国際学会「2008 IEEE International Electron Devices Meeting(IEDM 2008)」において7.5nm幅と小さいPRAMセル構造を発表した。製造技術は20nm以下であり、書き込み時間は50nsであるとした。

Copyright © ITmedia, Inc. All Rights Reserved.