微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(8/10 ページ)

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000 年代に入り、状況が変わってきた。

第3部 不揮発性ロジックで消費電力削減

第1部で述べたように、強誘電体や磁性材料をロジック回路と組み合わせることによって得られる利点は、MOS FETのしきい値電圧Vthのばらつき対策以外にもう1つある。電源電圧を下げることなく、消費電力の削減が可能になる点である(ロームが業界で初めて製品化した強誘電体カウンタに関しては、別掲記事「ロームが強誘電体ロジック投入、業界初の歴史を語る」を参照)。

ロジック回路を不揮発化して、動作させていない部分の電力供給を止めることで、待機時の消費電力を減らせる。強誘電体や磁性体は電力供給を止めても、その状態を保持するため、再び電力を供給すると、すぐに回路が動作する。

微細化を進める際の障壁は複数あり、その1つは消費電力の増大である。国際半導体技術ロードマップ2007年版の日本語訳には、「低電力デバイスのオフ時の消費電流は、製造技術の世代が進むごとに10%ずつ増加している」、「消費電力は緊急で短期的な技術課題」といった文言が並ぶ。

電源電圧を下げれば消費電力を削減できるものの、第2部で述べたようにMOS FETのVthのばらつきの問題などがあり、電源電圧はなかなか下がっていない。不揮発材料をうまく使えば、微細化によらず消費電力を大きく削減できる可能性がある*1)。

演算部とメモリーを融合

東北大学電気通信研究所の羽生氏は、不揮発性材料をロジックに導入し、ロジック回路とメモリーを一体化させた「不揮発性ロジック・イン・メモリー」を業界で初めて提唱し、その研究開発に取り組んできた*2)。「現在、これまでに無かったさまざまな材料がLSIの製造に使われている。もはや、Si(シリコン)基板だからといって、Si材料だけにこだわる理由はない」(同氏)という。

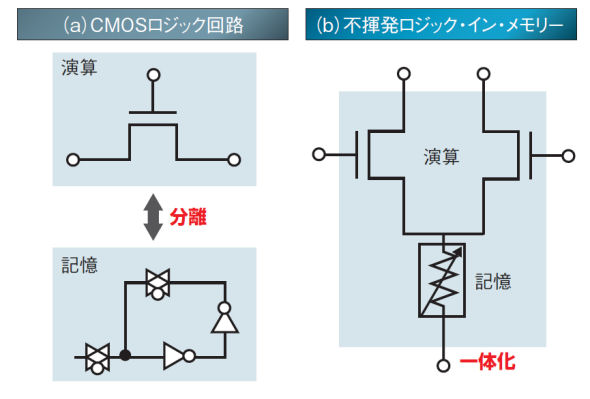

まず、電源を切った後にも情報を保持する仕組みがあれば、待機時の消費電力を抑制できる。さらに、情報を保持する部分をメモリーとして集中して配置するのではなく、ロジック回路(演算部)付近に分散配置する。こうすると、転送遅延の発生といった、ロジック回路とメモリーを接続する配線(グローバル配線)の悪影響も発生しない。配線部分の面積も削減できる。これが、同氏が提唱する不揮発性ロジック・イン・メモリーの基本的な考えだ(図1)。

図1 「不揮発性ロジック・イン・メモリー」を提案 東北大学電気通信研究所の羽生貴弘氏の研究グループは、(a)のようにロジック(演算)部とメモリー(記憶)部を分離するのではなく、(b)のようにロジック部とメモリー部を一体化させ、メモリー部を不揮発化した不揮発性ロジック・イン・メモリーの開発を進めている。

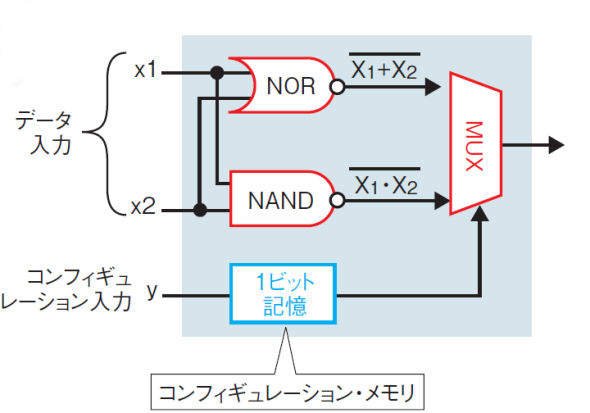

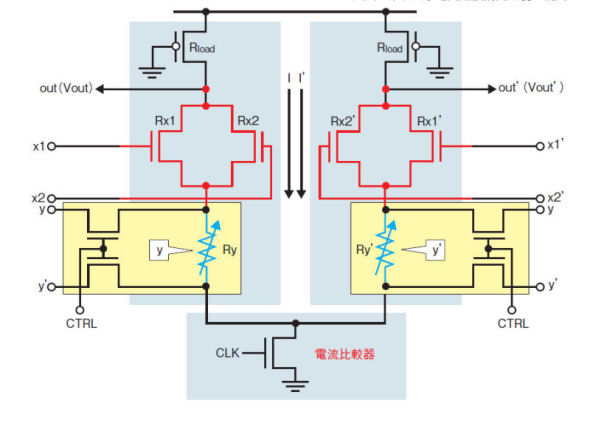

同氏の試みは、LSIに集積したフリップ・フロップやSRAMといった揮発性メモリーを、単に不揮発化するものではないことに注意する必要がある。新材料と回路技術の融合で、「演算」と「記録」を一体化させた回路の実現を目指しているのだ。ロジック回路の情報を保持させるMTJ素子は、1ビットの情報を保持する記憶回路になるとともに、演算回路を構成する一部分となる(図2、図3)。

図2 NANDとNOR、記憶回路を一体化 不揮発性ロジック・イン・メモリーのアイデアは、図中に示したNANDやNOR、マルチプレクサ、記憶回路を、それぞれのブロックで構成するのではなく、回路全体で実現しようというもの。 出典:東北大学電気通信研究所羽生研究室

図3 NANDにもNORにもなる 不揮発性ロジック・イン・メモリーのアイデアに従って、図2を実際の回路に展開した。情報を記憶するMTJ素子(図中の黄色の部分)が演算回路の一部となっている。MTJ素子の状態(「y」が0または1)を変えることで、回路全体をNANDまたはNORに切り替えられる。出典:東北大学電気通信研究所羽生研究室

Copyright © ITmedia, Inc. All Rights Reserved.