微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(9/10 ページ)

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000 年代に入り、状況が変わってきた。

FPGAへの展開を視野に

羽生氏の研究グループでは、不揮発性ロジック・イン・メモリーが適用できる典型例としていくつかの回路に注目し、実際の回路をすでに試作している。

MTJ素子は配線層の上部に積層する。回路を不揮発化するためにトランジスタ層の製造技術を改良する必要はない。LSIにおいて、MOS FETを形成したトランジスタ層とその上の配線層のうち、トランジスタ層は製造技術の共通化が急速に進んでいる。このため、「トランジスタ層を形成するフロントエンド工程で新材料を導入するよりも、配線工程で新材料を導入する方が容易」(NECのデバイスプラットフォーム研究所の研究統括マネージャーを務める笠井直記氏)だという。

具体的には、動きベクトル検出回路や、メモリーの一種であるTCAM (Ternary Content Addressable Memory) 回路、FPGA (Field Programmable Gate Array)を構成するルックアップ・テーブル(LUT)の不揮発版を試作し、動作を検証した。2入力LUTを例にすると、LUTを構成するSRAMを単に不揮発化したタイプに比べて、実装面積と動作時の消費電力を削減できることを確認した。

例えば、SRAMを単に不揮発化したタイプとしては、SRAMとMRAMの組み合わせや、SRAMとMTJ素子の組み合わせがある。前者の実装面積が455μm2、後者の実装面積が702μm2だった。これに対して、MTJ素子を使ってメモリーとロジック回路を一体化させた回路の実装面積は287μm2だった。また、動作時の消費電力は、それぞれ22.5μW、26.7μWだったのが、17.5μWに減った。いずれのタイプも、不揮発性LUTなので、待機時に電力を供給する必要はなく、消費電流はゼロに抑えられる。

昔のアイデアが新材料で結実

ロジック回路付近にメモリー部を分散配置するロジック・イン・メモリーの考えは、1969年にすでに提唱されていた。ロジック部とメモリー部のデータ転送のボトルネックを解消できるメリットがあるものの、Si材料のトランジスタのみでロジック・イン・メモリーを構成しようとすると、かえって回路規模が大きくなるという課題があった。

このため現在のLSIでは、ロジック回路(演算部)の処理結果を保持するために、フリップ・フロップ( カウンタ)回路やSRAM、DRAMをメモリーとして集中的に配置するのが一般的だ。羽生氏は、不揮発性でアクセス速度の高いことが特徴のMTJ素子をロジック回路に導入することで、不揮発性ロジック・イン・メモリーを初めて実証できたとする。MTJ素子は、東北大学電気通信研究所ナノスピン実験施設の教授である大野英男氏の研究グループが開発したものを使った。

今後、これまでより大規模なロジック回路の開発に取り組む。「5年程度で、実用化が視野に入る段階まで回路を作り上げる」(羽生氏)。設計ツールの作成も含め、実用化を強く意識した研究を推進する考えだ。

金属析出をスイッチに利用

ロジック回路に組み込める不揮発性材料は、強誘電体や磁性体だけではない。NECは、固体電解質中の金属架橋を不揮発性スイッチとして利用する開発を進めている(図4)。金属架橋が形成されて抵抗が下がった状態をオン、金属架橋が溶解した高抵抗状態をオフに対応させる。

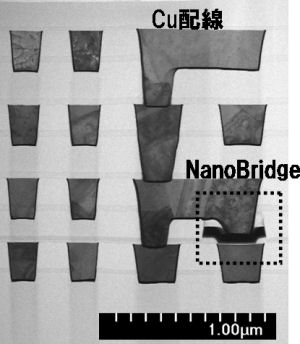

図4 金属の析出現象を利用した不揮発性スイッチ NECは2001年から金属の析出/溶解による抵抗値の変化を利用した不揮発性スイッチの開発を進めてきた。2009年には、新たな材料を採用することで、スイッチ特性を落とさずに、配線層内部に集積することに成功した。

金属の析出と溶解は、固体電解質に印加する電極の極性で切り替える。オン状態のときの抵抗は100Ω以下、オフ状態のときの抵抗は109Ω程度である。いったん形成した金属架橋は、極性が異なる電圧が印加されない限り溶解しないので、不揮発性スイッチとして使える。

同社はこの不揮発性スイッチを「NanoBridge」と名付け、2001年から研究を進めてきた。その後継続的に研究を進め、2009 年にはCu(銅)配線層中に集積することに成功した。

これまでは、Cu配線層内部にNanoBridgeを集積することが難しかった。高温(400℃程度)の熱処理などが原因で、スイッチ特性が劣化してしまっていたからだ。「新たに、固体電解質にTiO2(酸化チタン)とTaSiO(酸化ケイ素タンタル)を使用することで、配線工程中の熱やプラズマによるCu電極の酸化やCu原子の固体電解質への熱拡散を抑えた。その結果、歩留まりやスイッチ特性を改善できた」(NECデバイスプラットフォーム研究所の主任研究員である阪本利司氏)とする。

NanoBridgeの形状は直径が10nm 〜30nm、高さが10nm 程度で、TaSiOの固体電解質をRu(ルテニウム)電極とCu電極で挟んだ素子構造を採る。「これらの材料は、LSIの製造工程に適合する」(同氏)という。

NanoBridgeを形成するには、配線工程でマスクを2枚追加することになる。製造コストが増えることを意味するが、「例えば、先端製造技術を採用したFPGAのマスク数は40枚に達する。マスクを2枚追加することによる影響は全体の5%で、許容できる範囲だろう。マスク数が少し増えたとしても、多くのメリットがあるので、受け入れられるはずだ」(同氏)と説明した。

次世代FPGAへの搭載狙う

同社は、NanoBridgeの主な用途として、FPGAを構成するSRAMとパス・トランジスタ(再構成用スイッチ)の置き換えを挙げる。SRAMとパス・トランジスタがFPGA 全体の面積に占める割合は80%に達することがあるという。FPGAのさらなる高性能化には、SRAMとパス・トランジスタの改善が重要との考えである。

「NanoBridgeを使えば、SRAMとパス・トランジスタを不揮発化できるだけではなく、スイッチの低抵抗化や配線長の短縮に効果がある」(阪本氏)。FPGA 向けプログラマブル・スイッチは、オン/オフ比が106以上と大きく、スイッチ寸法や漏れ電流が小さくなければならない。NanoBridgeはこの条件を満たすという。書き換え回数は103程度と、ほかの材料に比べて劣るものの、FPGAでの利用を想定した場合は問題ないとした。

今後の課題は、スイッチごとの特性ばらつきの抑制と、信頼性の向上である。FPGAのスイッチ数は膨大で、スイッチそれぞれのばらつきの抑制が重要だ。経年劣化に対する耐性も確認する必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.