第20回 差動対がオペアンプに変身(5)〜コンデンサを追加して位相補償〜:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

前回に続き今回も、増幅回路の周波数特性を改善する方法を解説します。安定して動作するオペアンプを設計する上で重要なことは、十分な位相余裕と利得(ゲイン)余裕を確保することです。

まだまだ改善は続く

以上で、基本的なオペアンプの設計作業は終了です。ただ、実際に製品として世の中で使われているオペアンプには、これまでに紹介してこなかったさまざまな工夫が盛り込まれています。実際の製品には、どのような特性が改善されているのか、簡単に紹介しましょう。

まず、今回紹介したオペアンプの位相補償の方法は、コンデンサを1つ追加するというものでした。ですが、実際の回路設計では、応答速度をできるだけ遅くさせずに位相余裕を確保するために、複雑な位相補償回路技術が使われています。

また、製品として世の中で使われているオペアンプには、入力信号範囲にほとんど制限がありません。すなわち、入力信号は、ほぼグラウンド(GND)から電源電圧の範囲で動作します。これを、レールトゥーレール(Rail to Rail)と言います。

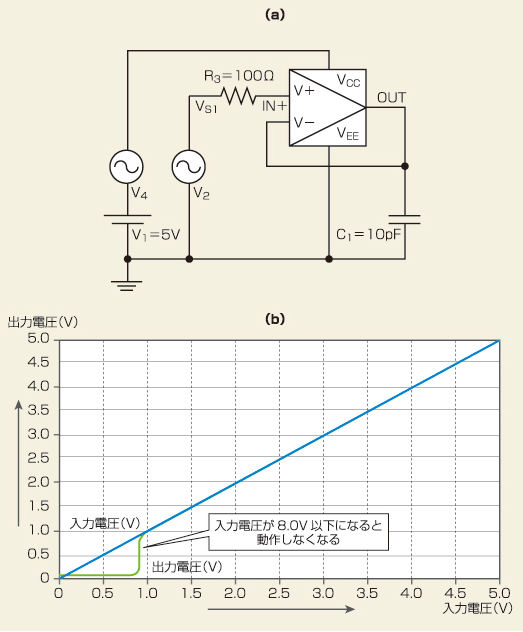

これに対して、今回までに設計したオペアンプは、レールトゥーレール動作に対応しているとはいえません。今回のオペアンプを、図3(a)に示したボルテージフォロアとして使った結果を図3(b)に示しました。入力電圧が0.8V 以下の領域では動作しなくなっていることが分かります。出力電圧はグランド電圧まで動作することを本連載の第18回で確認していますので、この原因は入力電圧が制限されていることです。

図3 基本形のオペアンプにはまだ改善が必要 今回までに設計した基本的なオペアンプの動作を確認するために、オペアンプをボルテージフォロアとして動作させました(a)。(b)はボルテージフォロアの入出力の直流特性です。入力電圧(青)が0.8V以下だと出力電圧(緑)が追従せず、動作していないことが分かります。

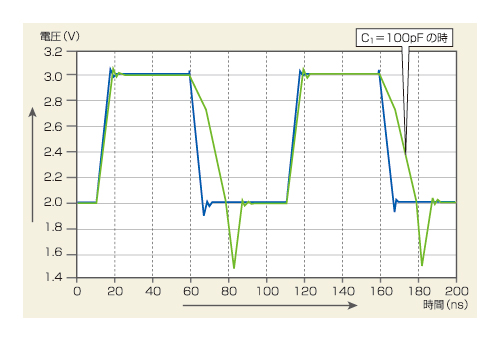

さらに、今回のオペアンプを使った場合、図3(a)の負荷容量を大きくすると、出力信号の波形が大きく乱れてしまいます(図4)。図4は、負荷容量の値を1pF、10pF、100pFと変えた時の出力信号です。負荷容量が100pFのとき、出力波形の立ち下がりのみが大きく遅れ、立ち上がりと立ち下がりの波形が非対称になっています。

図4 負荷容量の範囲も制限 図3(a) の負荷容量を1pFから10pF、100pFと変化させました。すると、負荷容量は100pFのとき、出力波形が大きく乱れていることが分かります。オペアンプの基本形は図1の通りですが、実際の製品として使うには、まだまだ改良を続けていくことが必要です。

これは、オペアンプの出力回路の駆動能力(今回説明したケースでは、出力電圧を下げる能力)が不足しているためです。これでは、使用できる負荷容量に制限があることになってしまいます。実際に製品として販売されているオペアンプでは、このような現象は発生しません。

レールトゥーレール動作に対応させ、出力信号の波形を非対称にさせないための回路の概略を紹介しましょう。レールトゥーレール動作させるためには、入力段にNPN型の差動対だけではなく、PNP型差動対も追加して、全入力電圧範囲に対応させる方法が一般的です。

出力信号の波形が非対称になることを防ぐためには、オペアンプの出力部分に「プッシュプル(Push Pull)」と呼ぶ方式の回路を使います。

プッシュプルとは、「押したり引いたり」する方式です。基本形である図1の出力段のNPN型トランジスタQ8は定電流源として動作しているため、入力電圧がどのような値であれ、一定の電流しか流しません。その結果、一定の電流で動作できる速度以上では動作しないことになります。これに対して、プッシュプル方式を採用したオペアップでは、入力電圧に応じて流せる電流が変わります。この違いが、立ち上がりと立ち下がりの波形の差となって現れています。

プッシュプル方式を採用した改良型のオペアンプでは、出力部の2つのトランジスタであるNPN 型トランジスタQ8とPNP 型トランジスタQ7はそれぞれ、入力電圧に応じて流す電流が変わります。ただし、Q7とQ8が両方とも同時にオン状態になってしまうと、膨大な電流(貫通電流)がQ7からQ8に流れて、消費電流が大きくなってしまいます。実際は、Q7とQ8のバイアス電圧を正確に制御し、貫通電流が流れないようにします。

このほか、オペアンプを製品化するときには、製造時の特性ばらつき(製造ばらつき)にも気を配る必要があります。特に、製造ばらつきに起因した入力オフセット電圧(入力オフセット電流)は、オペアンプの性能を左右する重要な項目です。さまざまなオフセットキャンセル方式が提案されており、オフセットを下げることに各社がしのぎを削っています。オペアンプの基本形は図1の通りですが、実際の製品として使うには、まだまだ改良を続けていくことが必要なのです。

これまでは、バイポーラトランジスタを使った回路設計を紹介してきました。次回から、電子回路に広く使われているCMOSトランジスタを紹介したいと思います。

Copyright © ITmedia, Inc. All Rights Reserved.