第26回 MOSFETで増幅器を設計(2):Analog ABC(アナログ技術基礎講座)(1/2 ページ)

本連載では、第24回以降バイポーラトランジスタからMOSFETに話題を移し、アナログ回路設計の基本を紹介してきました。今回は、前回に引き続き、MOSFETを使った増幅器の設計方法を解説しましょう。

本連載では、第24回以降バイポーラトランジスタからMOSFETに話題を移し、アナログ回路設計の基本を紹介してきました。今回は、前回に引き続き、MOSFETを使った増幅器の設計方法を解説しましょう。

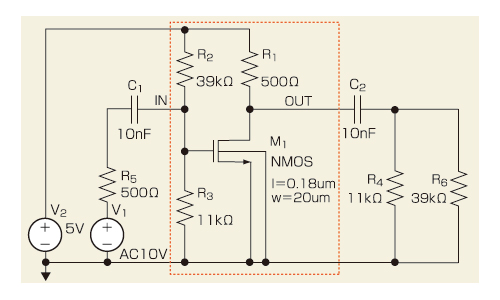

図1は、前回(25回)の結果を基にまとめた増幅器の回路図です。前回は、MOSFETの基本的な特性(ドレイン-ソース間電圧とドレイン電流の関係)のグラフに負荷直線を引き、バイアス点を求めました。バイアス点を決めれば、バイアス抵抗(図1のR2とR3)を設定できます。

利得「gm×R1」を算出

増幅器の特性を確認するために、図1では、MOSFETに電圧源や負荷抵抗を接続しています。電圧源の出力インピーダンスはドレイン抵抗R1と同じ500Ωに設定し、負荷抵抗であるR4とR6はゲートのバイアス抵抗であるR2とR3の並列抵抗と同じ値にしました。こうすることで、同じ増幅器を直列に接続したときに、どのような特性になるかをあらかじめ知ることができます。

まず今回は、図1の増幅器の交流(AC)特性を確認します。図1を見ながら、低域遮断周波数や利得を計算しましょう。

図1の信号源に接続するコンデンサ(C1)は、10nFに設定しました。増幅器の入力インピーダンスは、R2とR3の並列接続で決まり、下記の式(1)で計算できます。

増幅器の低域遮断周波数fcは、(1)式で求められる並列抵抗とコンデンサ(C1)で決まります。

利得は、MOSFETの相互コンダクタンスgm(単位は、ジーメンスS)と、負荷抵抗R1の積(gm×R1)で求められます。gmは、「ドレイン電流振幅/入力電圧振幅」なので、入力信号の振幅がどのくらいの係数で、ドレイン電流振幅に変換されるかを示しています。ドレイン電流振幅に負荷抵抗のR1をかけることで、入力信号振幅がどのくらいの出力信号振幅に変換されるか、つまり利得が分かります。

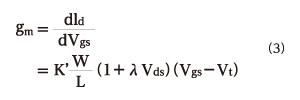

まず、利得を求めるためにgmを、下記の(3)式を使って計算します。この式は、前回(第25回)の(2)式に紹介したのと同じ式です。

今回のn型MOSFETの各パラメータは以下のように決めました。

- Vt=0.7

- K’=0.5e−3

- λ=0.02

また、前回のドレイン-ソース間電圧(Vds)とドレイン電流(Id)の曲線に引いた負荷直線の情報から、バイアス点のVds=2.7V、Vgs=1.1Vと読み取りました。以上の情報を(3)式に代入して、gmを計算すると、23.4mSになります。

従って、利得は23.4mS×500Ω=11.7倍=21.3dBになることが分かります。ただ、これはMOSFETだけの利得ですので、入出力抵抗による損失を差し引く必要があります。負荷抵抗のR2//R3(R2とR3の並列抵抗)と、出力抵抗R5で抵抗分割される分だけ利得が低下するため、損失分は以下のように計算できます。

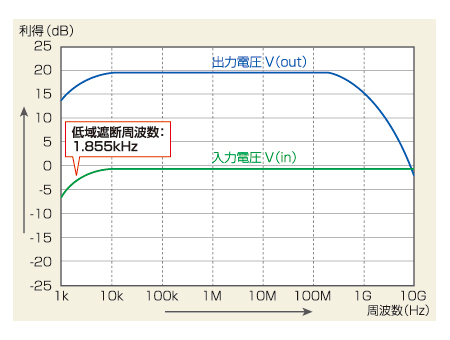

入力と出力の両方を合わせると、約1dBの損失になり、結果として全体の利得は約20dBになります。図2に、図1に紹介した増幅器に交流解析を施した結果を示しました。

図2 MOSFETを使った増幅器の周波数特性 図1の増幅器の交流(AC)解析の結果です。図中に示したとおり、利得が3dB下がる周波数である低域遮断周波数fcは1.855kHzです。fcは、増幅器の入力インピーダンス(R2とR3の並列接続)とコンデンサ(C1)で決まります。

一般に、すべての交流解析で注意すべき点は、動作点(DCバイアス)が正しいかということです。正しい動作点(あるいは目的の動作点)かどうかは、交流解析の結果からは分からないので、間違った動作点で実施した交流解析の結果を信じ込んでしまうと、その後の設計作業に大きな悪影響を与えてしまいます。

Copyright © ITmedia, Inc. All Rights Reserved.