「実はプレステ3で300万個の量産実績」、ソニーがコアレスパッケージの進展明らかに:実装技術 半導体パッケージ(1/2 ページ)

コアレス構造の半導体パッケージは、コスト低減や性能向上といったメリットがある一方で、安定した品質で大量に製造することが難しいとされていた。しかしソニーはすでに、民生機器用のLSIにコアレス半導体パッケージを適用し、大量に生産しているという。

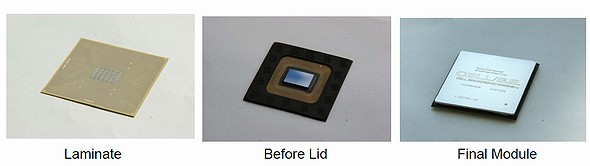

コアレス構造の半導体パッケージは、コスト低減や性能向上といったメリットがある一方で、安定した品質で大量に製造することが難しいとされていた。しかしソニーはすでに、民生機器用のLSIにコアレス半導体パッケージを適用し、大量に生産しているという。EE Times Japanに対して明らかにした。「実は、プレイステーション 3向けのCellプロセッサの量産に2010年4月から適用している。すでにコアレスパッケージ品の累積出荷数量は300万個を超えた」(同社の半導体事業本部 ハイブリッドシステムソリューション事業部 先端実装製品部で統括部長を務める大出和志氏)。コアレスパッケージ品でこのような大量生産に成功したのは、ソニーが世界初だと主張する(図1)。

現在のところこのコアレスパッケージ技術の適用先はソニーグループ企業の家庭用ゲーム機に向けたプロセッサにとどまっているが、「今後はネットワーク/通信機器用ASICをはじめとしたさまざまな応用を開拓していきたい」(同氏)と意気込んでおり、ソニーグループ外の顧客企業に向けて製造受託の形態での技術提供を視野に入れる。

図1 ソニーのコアレス半導体パッケージ 家庭用ゲーム機プレイステーション 3に使われるプロセッサ「Cell」用のパッケージとして大量生産に成功した。左はコアレスのラミネート基板。中央はベアチップをコアレス基板上に実装済みで、ふたをかぶせる前の状態。右は、パッケージの組み立てが完了した状態である。出典:ソニー

各社取り組むも量産化に大きな障壁

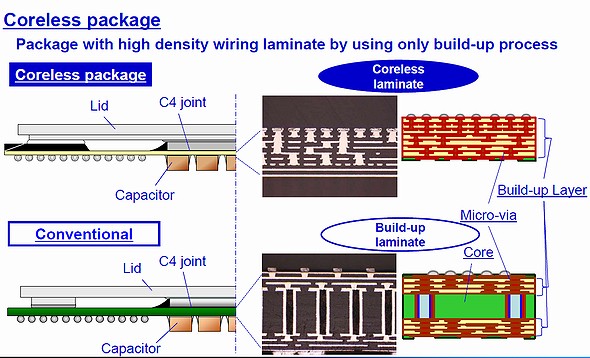

BGAタイプなどの半導体パッケージの内部では、一般にインターポーザと呼ばれる基板を使って、パッケージと半導体のベアチップを接続する(図2)。つまりインターポーザは、ベアチップを機械的に支持する機能と、チップ上の端子を再配線してパッケージの端子(プリント基板実装用のはんだボール)に電気的に接続する役割を担う。通常この基板は、機械的な強度を確保するための芯材(コア)を中心に挟んで、フィルム材料をビルドアップ工法で積層することで再配線層を作り込んでいる。

図2 コア基板/コアレス基板パッケージの構造の違い 上側はコアレス基板を使う場合、下側はコア基板を使う場合のパッケージの内部構造(左側)とインターポーザの構造(右側)である。コア基板では芯材(コア)を上下から挟むようにビルドアップ層を形成するが、コアレス基板はビルドアップ層のみで構成する。出典:ソニー

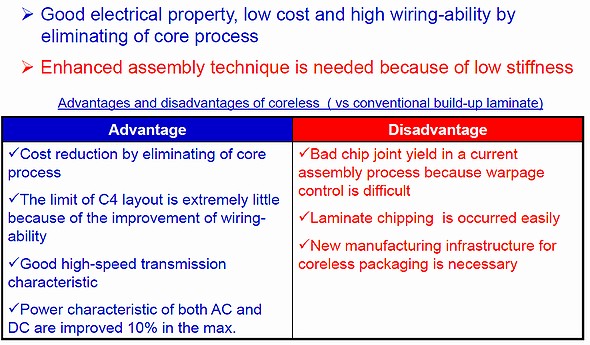

これに対しコアレス半導体パッケージは、コア材料を使わずにビルドアップ層だけを製造する。コアを形成するプロセスを省けるため基板のコストを削減できる他、通常はコアを挟んだ上下層の接続に不可欠なスルーホールが不要になるので、再配線経路の電気的特性が向上する、再配線経路の設計自由度が増加して配線密度も高まるといったメリットがある(図3)。そのため、コンピュータ用マイクロプロセッサやネットワーク/通信機器用ASICを手掛ける各社が開発に取り組んでおり、論文発表も数多くある。

ただし、コアレスはメリットばかりではない。デメリットもある。コアを用いないため、インターポーザ基板の機械的な強度を確保しにくいのだ。そのため基板の耐衝撃性が低下し、パッケージの組み立て工程で割れたり欠けたりしやすくなる。さらに、熱の影響による機械的な変位(反りや歪み)が大きくなり、ベアチップを基板に接続する工程の歩留まりが悪化してしまう。このためソニーによれば、「量産化が難しく、各社いろいろな試行錯誤を繰り返しているものの、なかなか立ち上がっていない」(大出氏)というのが実情だった。

Copyright © ITmedia, Inc. All Rights Reserved.