「実はプレステ3で300万個の量産実績」、ソニーがコアレスパッケージの進展明らかに:実装技術 半導体パッケージ(2/2 ページ)

コアレス構造の半導体パッケージは、コスト低減や性能向上といったメリットがある一方で、安定した品質で大量に製造することが難しいとされていた。しかしソニーはすでに、民生機器用のLSIにコアレス半導体パッケージを適用し、大量に生産しているという。

基板材料ではなく組み立て工程を改良

こうした課題を抱えながらも、コアレスパッケージには前述の通り確かなメリットがある。実際にソニーは、「Cellプロセッサにコアレス技術を適用した動機は、コストの低減だった。コア形成プロセスを省けるだけではない。基板の電気的な特性が向上して電源供給系のインピーダンスが低下するので、電源品質の確保のために実装するデカプリングコンデンサの数を、通常のパッケージに比べて減らせる。これらを総合すると、パッケージ関連のコストを15%〜20%削減できた」(大出氏)と明かす。

このようなメリットを享受するためには、何らかの方法で課題を乗り越える必要がある。しかし、コアレス化による機械的な強度の低下を材料の工夫で補うのは難しい。そこでソニーは、基板の材料を改善するのではなく、パッケージの組み立て工程を工夫するというアプローチを採った。「パッケージ技術には、材料とプロセスの2つの要素がある。一方で解決が難しいのならばもう一方で解決を試みる。今までパッケージ技術では、こうしたアプローチは必ずしも採られてこなかった。その観点で、パッケージ技術の分野には、改善の余地がまだたくさんあると感じている」(大出氏)。

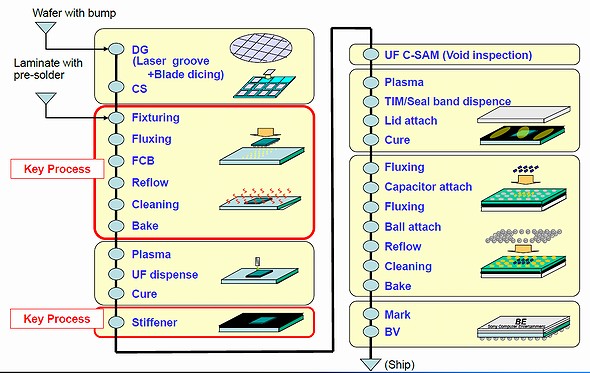

具体的には、2つの工程に工夫を施した(図4)。1つ目は、基板にベアチップをフリップチップで接続する工程である。「この工程では、リフローはんだ付けのために温度が大きく変化する。常温から260℃まで上昇し、再び常温に戻るといった具合だ。このように温度の変動幅が大きい場合でも、基板の平坦性を維持してフリップチップ実装の接続品質を安定させられるように、新たなプロセス技術を採用した」(同社の半導体事業本部 ハイブリッドシステムソリューション事業部 先端実装製品部で先端実装技術を担当する足立充氏)。ただし、採用したプロセス技術の詳細については、「ノウハウの固まりなので、これ以上は一切明かせない」(足立氏)としている。

2つ目は、フリップチップ実装後にアンダーフィル(封止用の液状硬化性樹脂)を塗布して硬化させる工程の後に、新たに追加した工程である。この工程では、基板の上に、あらかじめ用意しておいた薄いシート状のモールドコンパウンドを貼り付ける。ソニーはこのモールドコンパウンドを「スティフナー」と呼ぶ。基板の剛性を高め、基板のチッピング(欠け)を防ぐ役割を果たす。チップ部はくりぬいてあり、スティフナー自体の厚みはチップよりも薄いため、これでパッケージの厚みが増すことはない。スティフナーの材料は、「QFPなどの一般的なパッケージで使う樹脂材料を改良して用いた。熱膨張係数と弾性率について、パッケージを構成する基板とチップ、放熱用の銅版それぞれとの親和性を考慮するとともに、樹脂材料としての流動性も確保できるように配慮した」(足立氏)という。

図4 コアレス基板を扱うために組み立て工程を工夫 図中、赤色の枠で囲んだ2つの「Key Process」が、コアレスでの量産化を実現する鍵となった。2番目のKey Processであり、剛性確保のために「スティフナー」と呼ぶシート状のモールドコンパウンドを貼り付ける工程を、全工程の中でこのタイミングで実施している理由は、コスト的に最も有利だからだという。出典:ソニー

高速信号の伝送特性が向上

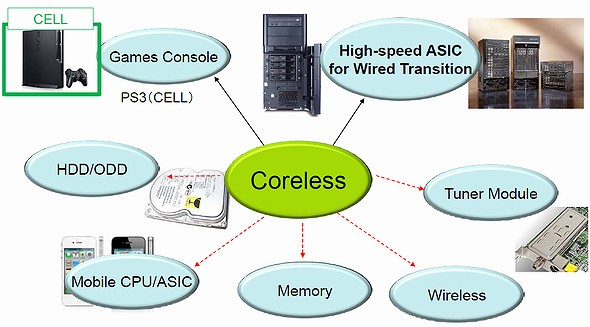

ソニーは、こうして量産レベルの製造性を確立したコアレス半導体パッケージの有力な応用分野として、大量のデータを高速に入出力することが求められるネットワーク/通信機器用ASICを挙げる(図5)。先に述べた通り、コアレス化によってパッケージの電気的な特性が向上するからだ。「コア基板を使う一般的なパッケージでは、コアを貫通するスルーホールによってインピーダンス整合が大きく劣化する。その結果、ベアチップの端子とパッケージの端子をつなぐ信号経路の反射損失(リターンロス)が増大し、品質を維持できる信号の速度が制限されてしまう」(足立氏)。

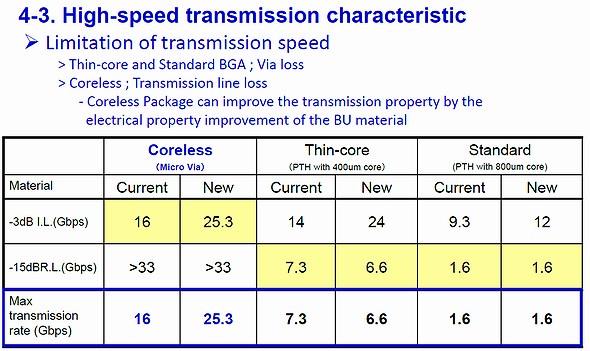

例えば、コアレスパッケージでは−15dBのリターンロスを確保できるデータ伝送速度の上限が33Gビット/秒を超えるのに対し、現状ではコアの厚みが400μmの基板を使うパッケージで7.3Gビット/秒、同800μmでは1.6Gビット/秒にとどまると言う(図6)。コアレス品では挿入損失(インサーションロス)がコア基板品に比べて大きくなる傾向があり、信号速度の制限要因になるものの、ソニーによればそれを考慮しても現状で16Gビット/秒を確保することが可能だ。さらに、「積層基板材料の誘電率などを改良すれば、25Gビット/秒まで高められる可能性があり、ハイエンドASICでデータ伝送速度が高まっていくトレンドに対応できる」(足立氏)とみる。

なお、このように電気的な特性は向上するものの、基板の設計ルールについてはコア基板を使う一般的なパッケージと変わらない。例えば、積層部の配線のライン/スペースは15μm/15μmである。

ソニーは、「まずは大手通信機器メーカーからハイエンドASICのパッケージ組み立て工程を受託する形で、コアレス半導体パッケージの社外への提供を始めたい」と話している(大出氏)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 モバイル端末向けパッケージング技術「FOWLP」(前編)

モバイル端末向けパッケージング技術「FOWLP」(前編)

ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程は、開発企業によって大きく異なる。そこで、いくつかに大別される製造工程の違いを紹介する。 キャパシターを忍ばせるパッケージ基板内蔵技術

キャパシターを忍ばせるパッケージ基板内蔵技術

富士通インターコネクトテクノロジーズは、「JPCA Show 2016」(2016年6月1〜3日/東京ビッグサイト)で、同年5月23日に発表した薄膜キャパシター内蔵技術を展示した。 Intelの高性能・高密度パッケージング技術「EMIB」の概要

Intelの高性能・高密度パッケージング技術「EMIB」の概要

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。 「プレステ4」を分解

「プレステ4」を分解

「プレイステーション3」から、7年を経て発売が開始されたソニーの最新ゲーム機「プレイステーション4」(PS4)。カナダのChipworksが、さっそく分解に着手した。 AMD、GPU/CPUの新ロードマップを発表

AMD、GPU/CPUの新ロードマップを発表

AMDは「CES 2018」のプレスカンファレンスにおいて、CPUとGPUのロードマップを発表。12nmプロセスCPUと7nmプロセスGPUの計画の詳細を明らかにした。