第30回 MOSFETのオペアンプを改善〜FET寸法の調整で入出力特性を向上〜:Analog ABC(アナログ技術基礎講座)(2/3 ページ)

前回は、MOSFETを使ったオペアンプの構成を紹介し、基本的な特性を解説しました。今回は、前回以降、これまでに設計したオペアンプの幾つかの問題点を、1つ1つ解決していきます。まず今回は、アンプをボルテージフォロアとして使うと、グラウンド電圧や電源電圧の付近において、出力電圧が入力電圧に追従できないという課題に取り組みます。

電源側での動作を分析

まず、GND電圧や電源電圧の付近では、入力と出力がずれてしまうという直流特性の問題に取り掛かります。図2の過渡解析の結果を見ると、出力電圧は十分にGND電圧と電源電圧に張り付いていましょう。このことから分かることは、オペアンプの出力段そのものには、十分な能力があるということです。問題の原因はどうやら、入力段にあるようです。

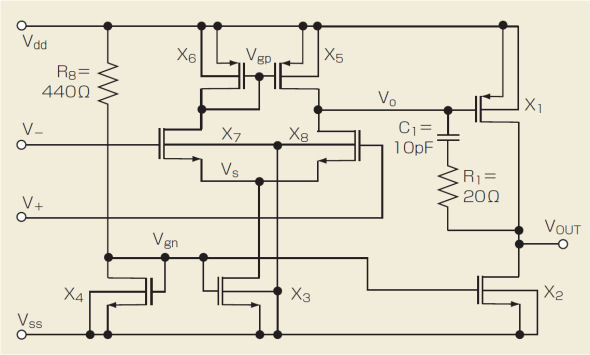

図3にこれまでに設計したオペアンプの回路図を示しました。原因を分析する上で、注目すべき電圧は、トランジスタX7とX8の接点部分の電圧Vsです。ここに注目して、各部の電圧や電流をプロットしたのが図4になります。

それでは、図3と図4を使いながら、原因を分析していきます。オペアンプをボルテージフォロアとして使っているということは、トランジスタX7のゲート電圧と、トランジスタX8のゲート電圧がほぼ等しくなります。なぜなら、ボルテージフォロアでは、入力電圧(V+)と出力電圧が等しく、出力は入力電圧(V−)と接続されています。

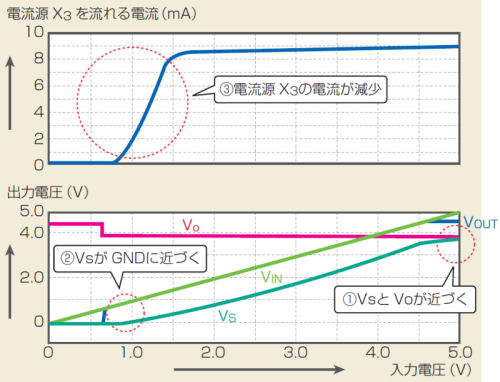

図4 図3の各部の電流や電圧 設計したオペアンプをボルテージフォロアとして使い、直流解析を実施した結果です。図上は、電流源X3を流れる電流値、図下は、トランジスタX7とX8の接点部分の電圧Vsや、トランジスタX1のゲート電圧Vo、入力電圧Vin、出力電圧VOUTです。グラウンドと電源付近で、入力電圧と出力電圧がずれています。

従って、図3のV+とV−はほぼ等しくなり、X7とX8のゲート電圧も等しくなります。その結果、入力電圧(V+)を電源電圧(Vdd)に近づけていくと、X7のゲート電圧も、X8のゲート電圧も、Vddに近づくことになります。ボルテージフォロアの回路図は、前回(第29回)の図4(a)を確認してください。

このとき、X7とX8のゲート-ソース間電圧(Vgs)は常にほぼ一定で、電流源X3によってX7とX8には一定の電流が流れています。このため、X7とX8で構成した差動対の両ゲート電圧がVddに近づくと、Vgsが一定であるため、ソース電圧VsもVddに近づくしかありません。

しかし、出力段のトランジスタX1のゲート電圧Voが、出力段に電流を流そうと電源から下がってきます。つまり、トランジスタX8のドレイン電圧Voとソース電圧Vsが近づき、Vdsが減少することになります(図4下図の(1)の部分を参照してください)。Vdsが減少するということは期待通りの電流が流れず、利得を失うことになります。このため、ボルテージフォロアとして使っているオペアンプの利得が減少し、それによって入力と出力の電圧にずれが生まれてしまうのです。

Copyright © ITmedia, Inc. All Rights Reserved.