Xilinxが28nm FPGAの消費電力ベンチマークを公表、「競合より50%以上も低電力」と主張:プログラマブルロジック FPGA(1/2 ページ)

28nm技術で製造する次世代製品群「Xilinx 7シリーズ」で採用した低消費電力化技術を紹介するとともに、各種のアプリケーションを想定した消費電力シミュレーションのベンチマーク結果も公表した。最大のライバルであるAlteraの28nm世代品に比べて、消費電力を大幅に低く抑えられると主張する。

FPGA大手ベンダーのXilinxは、28nm世代の半導体プロセス技術で製造する次世代製品群「Xilinx 7シリーズ」の低消費電力化技術に関する報道機関向け説明会を2011年6月27日に東京都内で開催した。7シリーズで採用したさまざまな低消費電力化技術とそれぞれの効果を紹介するとともに、各種のアプリケーションを想定した消費電力シミュレーションのベンチマーク結果も公表した。

来日中の同社アプリケーション&テクニカル マーケティング担当シニア ディレクタのリナ・ラーマン(Rina Raman)氏が説明にあたり、「今回のベンチマークでは、競合他社が提供する28nm世代のFPGAに比べて、FPGAの総消費電力が各種アプリケーションの平均で50%程度も低かった」と主張した。

同社は、2010年に7シリーズの開発方針を発表した段階で既に、「28世代品における最優先事項は、消費電力の低減である」と表明しており、「静的消費電力と動的消費電力を合わせた総消費電力を、40nm世代の現行品に比べて50%削減する」という目標を掲げていた。今回の説明会ではまず、この目標を達成したと報告した。

同社は2011年3月に、7シリーズの一部品種のエンジニアリングサンプル品を早期採用顧客に向けて出荷したと発表しており、同社内でもこのチップを使って消費電力の実機評価を進めてきた。この評価に用いたのは、同シリーズで用意する3つのファミリのうち、価格対性能比に最適化した「Kintex-7」で、集積規模が中程度の品種「K325T」である(参考記事)。40nm世代のハイエンド品「Virtex-6」と、このKintex-7に同じリファレンスデザインを実装して動作させたところ、Virtex-6では静的消費電力が3.6W、回路を稼働させたときの全消費電力が6.5Wだったのに対し、Kintex-7ではそれぞれ0.9W、3.1Wに抑えられたという。

今回の説明会で見せた消費電力比較デモの様子。左側が現行品「Virtex-6」の評価ボードで、右側が次世代品「Kintex-7」の評価ボード。それぞれの消費電力を実測したところ、Virtex-6では実装した回路が稼働していないときの静的消費電力が4.2W、稼働させたときが6.0Wだったのに対し、Kintex-7はそれぞれ1.0W、2.3Wに抑えられていた。

プロセスと各種の工夫で達成

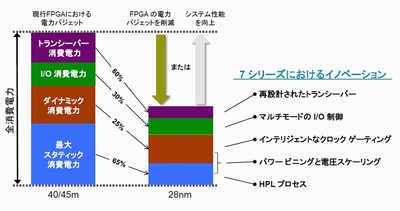

このような低消費電力化を実現できた理由としては、「低消費電力のFPGAに最適な製造プロセスを選択するとともに、さまざまな工夫を盛り込んだ」(ラーマン氏)ことを挙げた。プロセスについては、既に発表している通り、半導体ファウンダリのTaiwan Semiconductor Manufacturing Company(TSMC)が提供する高誘電体(high-k)/金属ゲートに基づく高性能・低消費電力の28nmプロセス「28HPL(High Performance Low Power)」を7シリーズの全製品に採用する。これが静的消費電力の低減に大きく貢献したという。後述する「パワービニング」と「電圧スケーリング」の効果と相まって、最大静的消費電力を65%削減できたと説明した。

この他、動的な消費電力については、次のようなさまざまな工夫を取り入れた。まず、高速シリアルトランシーバについて回路設計を見直した。その結果、高速シリアルトランシーバの消費電力をデータ伝送速度が同じ場合に約60%削減できたとする。また、入出力部についても、外部メモリにFPGAがデータを書き込んでいる間、使用しない入力バッファと終端回路を動的かつ自動的に無効化する機能と、メモリのアイドル期間に入力バッファと終端回路をオフにする機能を用意した。これによって、入出力部の消費電力を30%低減できたという。

加えて、クロックゲーティングの機能も高度化した。すなわちFPGAのロジック部にあらかじめ多階層のクロックゲーティング機構を搭載した上、XilinxのFPGA開発ツール「ISE(Integrated Software Environment)」にユーザーの設計データを解析してロジックの不要なスイッチングを抑制するアルゴリズムも組み込んだ。また、ブロックRAMについても、アドレスポートやデータ出力ポートの動作を解析し、その結果に基づいて動的に無効化できるようにした。次項で説明するパワービニングと電圧スケーリングの効果も含めると、動的な消費電力は25%低減できたという。

低消費電力グレードも新設

さらにXilinxは、ユーザーが購入時のオプションとして指定できる低消費電力グレード品も用意した。これまでも同社はFPGAのグレードとして、「C(コマーシャル)グレード」や「I(インダストリアル)グレード」などを取りそろえていたが、新たに「-2LE」と呼ぶ低消費電力グレードを追加した。一般にFPGAの製造では、動作速度は高いがリーク電流が大きいチップと、動作速度は低いがリーク電流が小さいチップの間で特性がばらつく。そこで同社は製造工程の選別で、一定の速度を確保できリーク電流がある程度以下に抑えられているチップを-2LEにグレード分けして供給する。これを同社は「パワービニング」と呼ぶ。なお-2LEの動作速度のグレード(スピードグレード)は中程度の「-2」に相当し、動作温度のグレードはCグレードの0〜85℃よりも広く、0〜100℃の拡張温度範囲に対応する。

-2LE品を選べば、Cグレード品に比べて静的な消費電力を45%削減できるという。さらに2LE品は電源電圧を標準の1.0Vから0.9Vに引き下げて動作させる電圧スケーリングにも対応しており、Cグレード品を1.0Vで駆動する場合に比べて、静的な消費電力を55%、動的な消費電力を20%それぞれ低減できると説明している。

Copyright © ITmedia, Inc. All Rights Reserved.