FPGAも並列コンピューティングの選択肢に、AlteraがOpenCLの取り組み発表:プログラマブルロジック FPGA

極めて高いプロセッシング性能を求めるアプリケーションでは、CPUにGPUやDSPなどのヘテロジニアスな計算資源を組み合わせてCPUの負荷をオフロードする並列コンピューティングの適用が進んでいる。Alteraは、オフロード用資源としてFPGAを選択肢に加える取り組みについて明らかにした。

FPGA大手ベンダーのAltera(アルテラ)は、並列コンピューティング向けソフトウェアプログラミングのフレームワークである「OpenCL(Open Computing Language)」を自社のFPGAに適用する研究開発プロジェクトを進めていると発表した。ハイエンドのビデオ処理システムや、医療イメージング機器、気候解析や金融モデリング向けの高性能コンピュータなどのシステムにおいて、メインプロセッサのソフトウェア処理負荷を軽減(オフロード)する並列コンピューティング用のアクセラレータとして、FPGAを利用しやすくする取り組みだ。同用途には既に、GPU(グラフィックスプロセッサ)やDSPが使われており、Alteraの取り組みが進展すればFPGAが新たな選択肢として加わることになる。

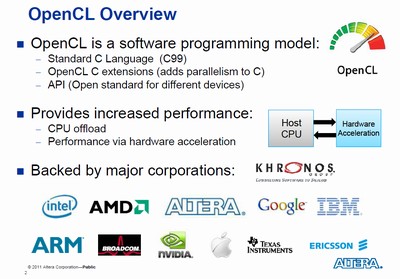

OpenCLは、CPUにGPUやDSPなどのヘテロジニアスな(異種混在の)計算資源を組み合わせて利用する並列コンピューティングに向けてC言語を拡張したプログラミングフレームワークで、業界コンソーシアムのKhronos Group(クロノス・グループ)によって標準化されている(図1)。オープンな規格であり、ロイヤリティーフリーで利用することが可能だ。メインプロセッサ上で稼働する標準的なC言語記述のプログラム(これを「ホストコード」と呼ぶ)と、アクセラレータ上で実行するOpenCL規格に準拠したC言語記述のプログラム(これを「カーネルコード」と呼ぶ)を連携させることにより並列コンピューティングを実現できる。

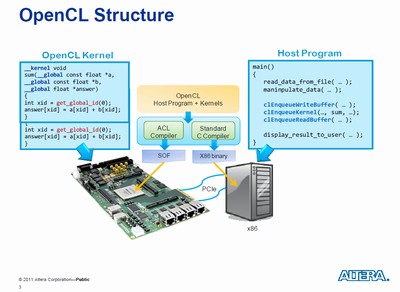

Alteraは、同コンソーシアムに約1年前に加入しており、複数の機器メーカーと協業してOpenCLのフレームワークをFPGAに適用する実証プロジェクトを進めてきたという。実際の適用方法は例えば次のようになる(図2)。まずメインプロセッサ用に開発したC言語プログラムをプロファイリングツールで解析し、演算負荷の重い部分を見つけ出す。次にその部分を切り出して、OpenCLに沿った拡張記述でカーネルコード化する。続いてカーネルコードをAlteraが用意した専用コンパイラで処理して、いったんハードウェア記述言語(HDL)のコードに自動変換する。それをFPGA開発ツールでコンパイルすることで、FPGAにハードウェアとして実装する最終的な書き込みファイル(SOF)を得る。ホストコードについては、標準的なCコンパイラでコンパイルしてメインプロセッサに実装すればよい。

図2 OpenCLの適用例 図中、「ACL Compiler」とあるのは、Alteraが自社FPGAに向けて用意するOpenCL対応の専用コンパイラといったニュアンスである。またこの図ではACL Compilerから直接、FPGA書き込みファイル(SOF)が出力されるように描かれているが、実際にはACL Compilerはいったんハードウェア記述言語のコードを出力する。それをFPGA開発ツールで論理合成してマッピングすることで、SOFが得られるという流れだ。出典:Altera

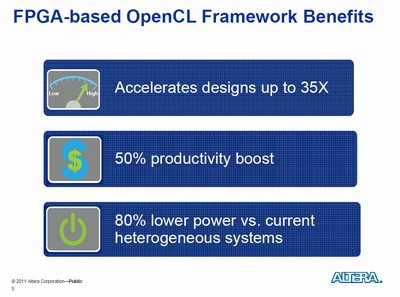

実証プロジェクトに参加しているある機器メーカーの事例では、ビデオ信号の圧縮処理にこのOpenCLのフレームワークを適用した。その機器メーカーはAlteraのFPGAユーザーであり、以前は圧縮アルゴリズムをまずC言語で開発し、それを手作業でHDLにコーディングし直してからFPGAに実装していたという。Alteraによれば、この企業はOpenCLのフレームワークを適用することで、HDLのハンドコーディングが不要になり、開発に費やしていた工数を50%削減できたとしている(図3)。

この他にもAlteraによれば、OpenCLを適用したFPGAをハードウェアアクセラレータとして使うことで、マルチコアCPU上でソフトウェアだけで処理する場合に比べて性能が35倍に高まった事例や、並列コンピューティングにおいてCPUと組み合わせるGPUをFPGAに置き換えることで消費電力を80%低く抑えられた事例があるという。

AlteraはこのOpenCLのフレームワークの適用形態として、ボード上でCPUとFPGAを連携させるシステムの他、さらにGPUやDSPも混在するシステムや、2011年10月に発表したARMコア混載FPGA「SoC FPGA」のチップ上でARMコアをメインプロセッサとし、FPGA部をハードウェアアクセラレータとするシステムも視野に入れている。ただし、このフレームワークに向けたプロファイリングツールやOpenCL準拠のFPGA専用コンパイラについては、製品化するかどうかも時期も未定だという。今後、実証プロジェクトに参加している企業のフィードバックを受けて、検討を進めるとしている。

関連キーワード

FPGA | アルテラ | OpenCL | GPU | ソフトウェア | C言語 | CPU | ARM | DSP(Digital Signal Processor) | Khronos Group | プログラミング | API | GPGPU | GPUコンピューティング

Copyright © ITmedia, Inc. All Rights Reserved.