Intelが「Ivy Bridge」の技術を発表、160mm2に14億のトランジスタを集積:ISSCC 2012

Intelは、「Sandy Bridge」の後継となる「Ivy Bridge」の技術的な詳細をISSCC 2012で発表した。同社が描く「テラスケールクラスのクライアント」への一歩になる。

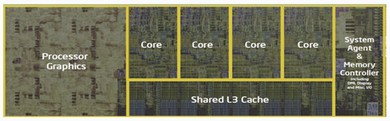

Intelは、3次元ゲート(Tri-Gate)構造のトランジスタ製造技術を採用した22nmプロセスの新型CPU「Ivy Bridge」について、その詳細を公表した。同社は、主要な品種を少なくとも4種類とりそろえる予定で、最もサイズが大きい品種では、160mm2のチップ面積に14億個のトランジスタを集積するという。

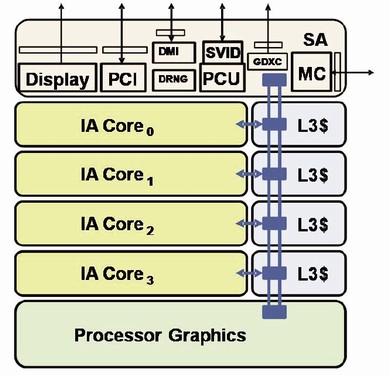

Ivy Bridgeは、インターコネクト用のPCI Express(PCIe) Gen3を20チャンネル備え、DisplayPortのコントローラも集積している。Intelは、Ivy Bridgeを市場に投入することにより、同社が「テラスケールクラスのクライアント」と表現する長年の目標の実現に向け、小さな一歩を踏み出すことになる。

Ivy Bridgeの最初の品種は、デスクトップPCやノートPC、組み込みシステム、最大8Mバイトのキャッシュを備えた単一ソケットのサーバシステムなどの用途に向けるという。Intelの前世代品と同様に、メモリコントローラとグラフィックス処理回路を搭載するほか、DDR3L DRAMのサポートや、MicrosoftのAPI(Application Programming Interface)「DirectX 11」のサポートも実現している。

IntelのエンジニアであるScott Siers氏は、2012年2月19〜23日に米カリフォルニア州サンフランシスコで開催されている半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference)2012」で論文を発表し、「当社はこのチップの設計に当たり、派生品種を短期間で開発できるように、モジュール性の確保にかなりの時間を費やした」と語った。

最もサイズが大きいチップは、x86コアを4つと、大型のグラフィックス処理ブロックを1つ集積する。これを自動生成ツールを使ってx軸およびy軸に沿って分割し、2コアの品種や小型のグラフィックス処理ブロックを集積した品種を用意することも可能だという。

Siers氏によると、Ivy Bridgeは、駆動電圧が1.35Vの低電圧版DDR3Lをサポートするほか、スタンバイモードにおけるDDRのパワーゲーティングも採用している。また、最大で1600Mトランスファ/秒をサポートし、1.5VのDDR3にも対応する。

DisplayPortブロックには、1.6GHz/4レーンが1つと、2.7GHz/4レーンが2つ搭載されており、3つのディスプレイまでサポートする。

PCIeブロックは、レシ−バ部に32段階の利得制御レベルを備えたCTLE(Continuous Time Linear Equalization)を採用したほか、トランスミッタ部には3タップのFIR(Finite Impulse Response)フィルタを搭載している。またこのPCIeブロックは、ジッタのオンダイテスト機構を組み込んでいる上、タイミングや電圧マージンの測定などにも対応する。

Ivy Bridgeはチップ全体で5つの電源プレーンを備え、個別にゲーティング可能な180個のクロックアイランドをサポートしている。

また、IntelでCPO(最高製品責任者)を務めるDadi Perlmutter氏は、ISSCCの基調講演に登壇し、テラヘルツクラスのクライアントについて、長期的な展望を語った。同氏によれば、テラヘルツシステムの消費電力は、現在約3kWであるが、さまざまな技術を適用すれば、10年後には20Wにまで低減できる可能性があるという。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.