「ファブレスモデルは崩壊する可能性も」、Intelの幹部が指摘:ビジネスニュース

Intelは同社のプレスイベントにおいて、「半導体プロセスの微細化が進むほど、ファブレスモデルを維持することは難しくなるのではないか」との見解を示した。同社は、プロセス技術の開発者と、チップの設計者が密に連携できる体制が必要だと主張する。

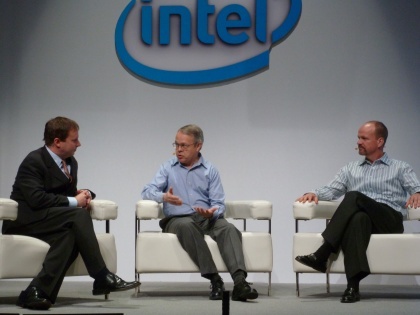

Intelでプロセス技術開発を主導するMark Bohr氏によると、「ファブレスモデルの終えんが訪れようとしている」という。

Bohr氏は、22nm世代の3次元ゲート(Tri-Gate)構造トランジスタ技術を適用して製造した新型CPU「Ivy Bridge」の発表イベント(2012年4月23日)で、「TSMCは2012年4月17日に、20nmプロセスの製品ラインアップを1種類のみにすると発表したが、これによって同社は開発の失敗を露呈した形となった。TSMCは、次世代ノードでは、3次元ゲート構造トランジスタ技術を適用できないとみられる」と語った。なお、3次元ゲート構造トランジスタは、リーク電流に起因した消費電力を低減できると期待される技術である。

同氏は、TSMCに製造を委託しているQualcommについて、「20nmプロセスを適用した製品を製造できない可能性もある」と指摘、「ファウンドリモデルは崩壊しつつある」との見解を示した。

Intelは、TSMCやGLOBALFOUNDRIESなどのファウンドリ企業の追随を許さず、世界が必要とする複雑な半導体技術を生み出せる唯一の企業となることを目指している。なお、GLOBALFOUNDRIESは、Intelにとって最大のライバル企業であるAMD(Advanced Micro Devices)から、半導体製造を請け負っている。

Intelは、Ivy Bridgeの発表イベントで「Ivy Bridgeの開発成功の陰には、プロセス技術の開発者とチップの設計者との密接な連携がある」と語った。

IntelのクライアントPCグループで新しくゼネラルマネジャーに就任したKirk Skaugen氏は、「プロセス技術の開発者であるBohr氏と、Ivy Bridgeのプログラムマネジャーを務めるBrad Heaney氏は、Ivy Bridgeだけでなく、Intelで初めて高誘電率膜/金属ゲート(HKMG:High-k/Metal Gate)技術を採用したプロセッサを開発した際も、密な連携を取っていた」と述べている。

Bohr氏は、「垂直統合型半導体メーカー(IDM:Integrated Device Manufacturer)であることは、小型で複雑な半導体チップの開発で発生するさまざまな問題の解決に役立つ」と主張する。

この点については、筆者も全く反論はない。EE Timesは、μm以下のプロセスの設計が始まった当初から、「チップの設計者とプロセス技術の開発者の間で、より密接な連携が必要になる」と説いてきた。NVIDIAで物理設計を担当するある幹部社員も、最近実施されたMentor Graphicsのユーザーグループの年次会議で、Bohr氏と同様の見解を述べていた。

だが、「ファウンドリやファブレス企業はIntelに続くことはできない」とまで言うのは、Bohr氏の言いすぎではないだろうか。筆者は、TSMCのトップとGLOBALFOUNDRIESの研究開発マネジャーに話を聞いた。彼らは、「14nm世代までは3次元ゲート構造トランジスタは必要ない」と述べている。しかし、実際のところTSMCは、20nmプロセスでは高性能と低消費電力の製品間で顕著な差をつけられず、製品ラインアップを1種類しか用意することができなかった。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連キーワード

Intel | TSMC | プロセス技術(エレクトロニクス) | Ivy Bridge | 設計 | 20nmプロセス | ファブレス | GLOBALFOUNDRIES | high-kメタルゲート | 垂直統合 | 28nmプロセス | ビジネスニュース(EE Times Japan)

Copyright © ITmedia, Inc. All Rights Reserved.