CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発:ISSCC 2013(2/2 ページ)

富士通研究所は、CPU間のデータ通信速度を従来比で約2倍となる32ギガビット/秒(Gbps)に高速化できる送受信回路を開発した。次世代サーバ向けCPUに適用し、2014年ごろの実用化を目指す。

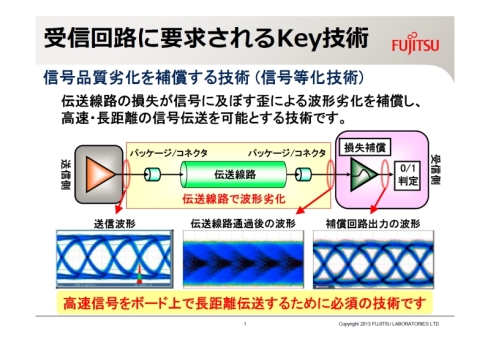

損失補償回路で伝送距離を確保

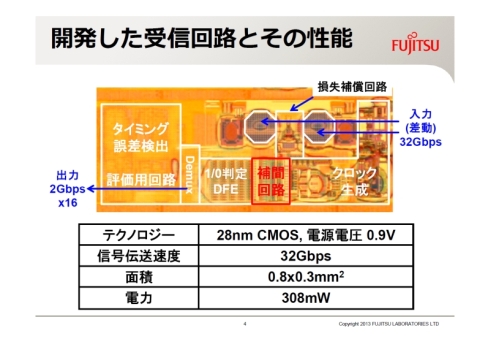

プリント配線板などの伝送路では、信号品質が劣化する。伝送する信号がより高速になったり、伝送距離が長くなったりすれば、その信号損失は大きくなる。そこで、富士通研究所と米子会社のFujitsu Laboratories of Americaは、データ通信速度を32Gbpsまで向上させた場合でも、80cmのデータ伝送距離を実現できる損失補償回路を開発した。

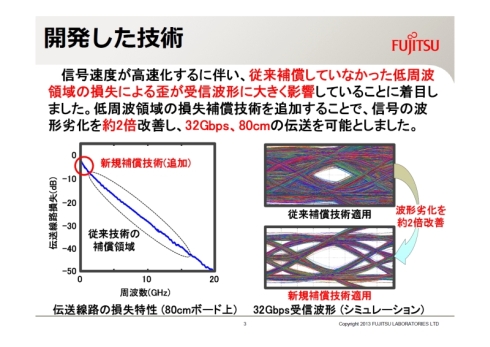

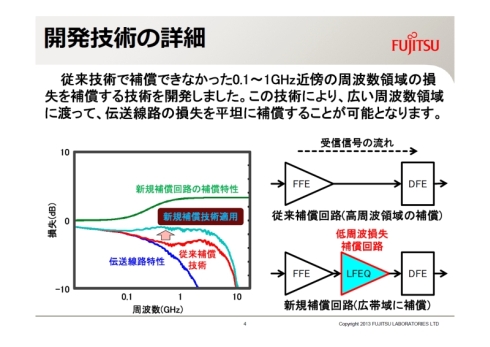

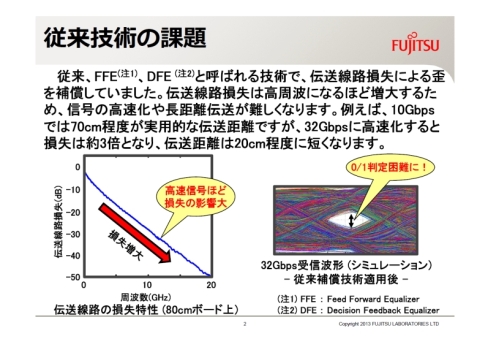

これまでの損失補償回路では、伝送線路損失による歪み(ひずみ)を補償するために、FFE(Feed Forward Equalizer)やDFEといった回路技術を用いてきた。しかし、データ通信速度の高速化によって、これらの回路技術だけでは損失を補正することは難しくなっている。例えば、データ通信速度が10Gbpsであれば、70cm程度と実用的な伝送距離を確保できる。ところが、32Gbpsまで高速化すると、伝送路での損失は約3倍に増えて、伝送距離も20cmと短くなってしまう。

FFE(Feed Forward Equalizer)やDFEを用いる損失補償回路では、データ通信速度を32Gbpsまで高速化すると十分な伝送距離を確保できない(クリックで画像を拡大) 出典:富士通研究所

このような課題に対して、高速信号になれば低周波領域の損失による歪みが受信波形に影響してくることに着目。そこで、これまでの技術では補償できなかった0.1G〜1GHz近傍の周波数領域における損失を補償する技術を新たに開発した(図3)。この技術を用いることで、32Gビット/秒のデータ伝送速度で80cmの伝送距離を実現することができた。広い周波数領域で伝送線路の損失を平坦に補償することが可能となったからだ。

データ補間方式を適用した受信回路

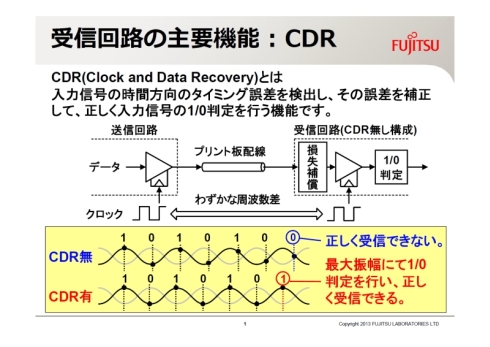

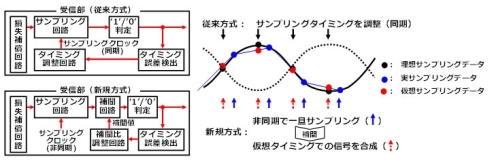

受信回路では、損失補償回路で整形された信号に対して、周波数とタイミング(位相)を同期させて信号をサンプリングし、元のデータを復元する。このとき、従来はタイミング誤差を元データから検出し、入力信号をサンプリングするためのタイミング調整を行っていた(CDR:Clock and Data Recovery)。しかし、データ通信速度が高速化すると、クロックを制御する時間精度をさらに高精度化する必要があるので、従来のCDRでは精度の高いタイミング調整が困難である。

そこで富士通研究所が開発したのが、データ補間(データインターポレーション)方式を適用した受信回路である。この方式はサンプリングクロックを同期させるのではなく、まず非同期のクロックで信号をサンプリングする。次にサンプリングした2つの信号を元に、電圧補間処理を行い、クロックと同期したタイミングで仮想信号を合成する。この方式を採用することで、高速化に対応することは難しいとされているタイミング調整が不要になった。32Gbps以上の高速化にも対応可能だという。

なお、これら3つの回路技術は、TSMCの28nmプロセスを用いて製造した試作チップによって動作を確認している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

スマホでPC画面を映すだけ、富士通研のファイル転送技術

スマホでPC画面を映すだけ、富士通研のファイル転送技術

富士通研究所は、スマートフォンやタブレット端末をPCの画面にかざすだけで、画面上に表示されているファイルがタブレット端末に転送される技術を開発した。「商用化はこれから」だとする同社だが、ビジネスシーンや私生活など、数多くの用途を想定している。 「最適な大きさで喋ろう」、富士通研が無線センサーの制御技術を開発

「最適な大きさで喋ろう」、富士通研が無線センサーの制御技術を開発

富士通研究所は、無線センサーネットワークを使ってより多くのデータを集められる手法を開発した。最大データ収集量が2.6倍に増えるという。データパケットの衝突を抑制することで実現しており、各センサーが送信出力、すなわち通信範囲を自律的に変えることで達成できた。 サーバからファンを外すとよく冷える、富士通が消費電力40%低減に成功

サーバからファンを外すとよく冷える、富士通が消費電力40%低減に成功

大型の機器を効率良く冷却するにはどうすればよいのか。これは組み込み機器、産業機器、IT機器などさまざまな分野にまたがる重要な課題だ。富士通は約100台のサーバを格納したコンテナデータセンターで、新しい「解」を探り当てた。