パナソニック、CMOS回路上での強誘電体メモリスタ形成に成功:プロセス技術

パナソニックは、アナログデータを記憶、再生できる「強誘電体メモリスタ」をCMOS回路上に形成することに成功したと発表した。

パナソニックは、アナログデータを記憶、再生できる「強誘電体メモリスタ」をCMOS回路上に形成することに成功したと発表した。同社では、「世界初の成果」とし「電子回路上で『人の思考』の一部を再現するニュートラルネットワーク処理に応用した場合、消費電力を最大1/10に削減できる」とする。

メモリスタとは、流れた電流量により抵抗値が変わり、その状態を保持する機能を持つ素子で、抵抗、コンデンサ、インダクタに続く「第4の受動素子」とされる。従来の「0,1」で記憶するデジタルメモリに対し、0〜1までの任意の中間値をアナログデータとして記憶、再生でき、より多くの情報を記憶できるという。パナソニックでは、強誘電体の材料を用いて、メモリスタに近い機能、動作を実現できる強誘電体メモリスタを2010年6月に発表していた。

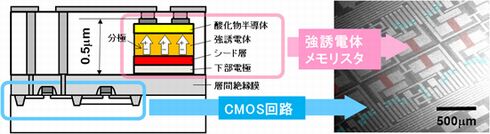

今回の成果は、この強誘電体メモリスタを、広くデジタル回路として用いられているCMOS回路上に形成したもの。これまで、CMOS回路上に強誘電体メモリスタを形成した場合、強誘電体の原子配列にゆがみが生じ、アナログデータを良好に記憶、保持できなかったという。これは、CMOS回路の最表面を覆う膜(シード層)が、隣り合う原子の配列が整合された状態で形成されていなかったことに起因した。

今回、パナソニックは、原子が規則正しく配列し、原子間の距離が強誘電体に近い数値を持つ材料をシード層として選択。強誘電体の結晶成長の方向が整い、結晶性の良い強誘電体メモリスタを形成することに成功したという。

同時に、パナソニックでは、「ニュートラルネットワーク回路」の実現に向け、入力されたデジタル信号をアナログ制御により演算した上で、結果を出力するハイブリッド回路設計技術も開発。ニュートラルネットワーク回路は、脳の神経細胞の信号処理の仕組みをモデル化した回路。その仕組みは、最初に、望んだ出力信号が得られるように、入力信号に対し抵抗値で重み付けを行って複数のデータを学習させた後、メモリスタの抵抗値が変化しないようにして判断したいデータを入力すると、学習させたデータ群の中から入力データに近いものが出力されるというもの。このニュートラルネットワーク回路の信号処理では、複数の演算素子間はデジタル信号であるパルス信号で接続され、演算素子内部ではパルス信号を電流として用いた演算処理を行う。パナソニックは、デジタルとアナログという異なる性質の演算処理をシームレスに行うハイブリッド回路の設計に成功したとしている。また、同社は「パターン認識処理に応用した場合、従来の1/10の消費電力で処理が行える」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

消費電力1/100に! 夢の“不揮発ロジック”の実用化へ前進

消費電力1/100に! 夢の“不揮発ロジック”の実用化へ前進

NECと東北大学は、スピントロニクス技術のロジックLSI分野への応用の道を開く2つの開発成果を発表した。2者は、「今回の開発成果をさらに進化させ、2017年頃には商用デバイスに技術を反映させたい」とする。 「あらゆる条件下で業界最小」、超低消費電力のFRAMマイコンが登場

「あらゆる条件下で業界最小」、超低消費電力のFRAMマイコンが登場

低消費電力マイコンとして知られる「MSP430シリーズ」に、消費電力を一段と引き下げた製品群が登場する。「Wolverine」と呼ぶ、FRAMマイコンの新たな製品プラットフォームを適用した品種で、第1弾のサンプル出荷を2012年6月に始める。- 「メモリスタの実用化は2009年」、HP社が抵抗変化型RAMに適用へ