ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」:プログラマブルロジック(2/2 ページ)

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。

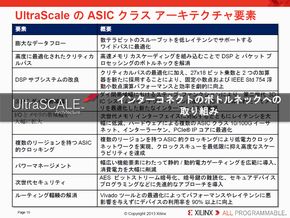

ASICクラスプログラマブルアーキテクチャ「UltraScale」とは

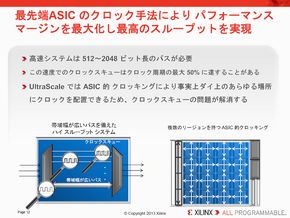

同社がアーキテクチャにこだわる背景には、FPGAの微細プロセス導入による高速化、高集積化が進展する中で、デバイス内部の接続性などアーキテクチャに関わる部分が性能向上のボトルネックとなっていることがある。「ロジック素子の集積度は、微細プロセス技術により、指数関数的に急増している。しかし、内部接続速度の進化は直線的であり、そのギャップは開くばかりだ。UltraScaleは、内部接続速度も集積度同様の伸長を実現するもの。最先端のASICのクロック手法を用い内部接続速度の問題を解消するなど、UltraScaleは『ASICクラスプログラマブルアーキテクチャ』と位置付けている」(ローガン氏)という。

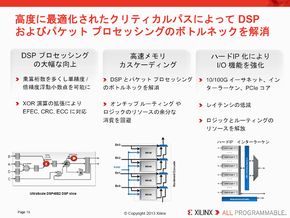

クロックスキューを解消

UltraScaleでは、ASICに多く用いられるクロック源をダイに分散して配置する手法を導入。これにより、クロックスキューと呼ばれるクロックのズレなどの問題を解消し、クロックを高速化できるという。また、DSPやパケットプロセッシングを高速化させる技術も複数導入する。DSPでは、乗算桁数を多くし単精度/倍精度浮動小数点演算を可能にした。また高速メモリカスケーディング技術により「DSPとパケットプロセッシングのボトルネックを解消する」(同社)という。10G/100GイーサネットやPCI ExpressなどをハードIP化しI/O機能なども強化する。

消費電力低減に向けても、1.2V動作DDR4メモリへの対応などを進めるといったハードウェア的な工夫を多数盛り込む他、開発環境「VIVADO」の消費電力最適化設計機能を強化するなど総合的な改良を進めている。

引き続きTSMCのプロセスを採用

採用する20nmプロセスは、28nm世代に引き続き、TSMCのプロセス技術(TSMC 20SoC)を採用した。

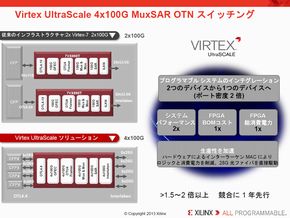

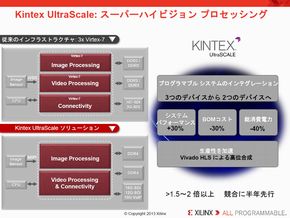

同プロセス導入に伴い、28nm世代に比べ最大35%の静的消費電力を削減できるという。ローガン氏は、「20nmプロセス、UltraScaleの適用により、実現可能なシステムレベル性能を従来比1.5倍から2倍まで高められる」としている。

「Virtex」「Kintex」「Zynq」への適用が決定

ザイリンクスでは、20nmプロセスとUltraScaleを導入した製品として、ハイエンド製品ファミリ「Virtex UltraScale」とミドルエンド製品ファミリ「Kintex UltraScale」の2ファミリを投入する方針。その後、CPU搭載型の「Zynq UltraScale」の投入も計画している。ただ、ローエンド製品ファミリ「Artix」へのUltraScale適用については「今日現在はコメントできない」(同社)とし、明らかにしていない。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

大手FPGAベンダーであるXilinxは、最先端の半導体製造プロセスを用いた製品開発に意欲的なことで知られている。同社は、TSMCの20nmプロセスを用いた次世代品を、2013年10〜12月期にサンプル供給する方針を既に明らかにしている。日本法人のザイリンクスで社長を務めるサム・ローガン氏に、通信機器におけるASIC/ASSPからFPGAへの置き換えの進展や、競合のAlteraが発表したIntelの14nmプロセス採用に対する見解などについて聞いた。 Intelの14nmプロセス技術を用いた「Stratix 10」を発表、年内にテストチップ出荷

Intelの14nmプロセス技術を用いた「Stratix 10」を発表、年内にテストチップ出荷

アルテラは次世代FPGA「Generation 10」として、Intelの14nmトライゲートプロセスで製造するハイエンド製品「Stratix 10」と、TSMCの20nmプロセスを用いたミッドレンジ製品「Arria 10」を発表した。Stratix 10は、現行のStratix Vに比べて性能が2倍となる。 2Tbps帯域幅のFPGAをザイリンクスが出荷、バックプレーン伝送波形も公開

2Tbps帯域幅のFPGAをザイリンクスが出荷、バックプレーン伝送波形も公開

高性能有線通信アプリケーション向けの新型FPGA「Virtex-7 X690T」の伝送波形を公開した。28nm世代の半導体技術で製造するハイエンドFPGAファミリ「Virtex-7」のうち、13.1Gビット/秒のSERDESを80チャネル搭載した品種である。3月下旬にサンプル出荷を始めたばかりだ。