Intelは9nm以降の技術を発表、IEDMのプログラムが決まる:ビジネスニュース

2013年12月に開催される半導体素子の国際学会「IEDM 2013」では、FinFETとFDSOIに注目が集まりそうだ。TSMCは16nm FinFETの他、14nmのFDSOIについて論文を発表するという。Intelは、9nm以降で用いるトンネル電界効果トランジスタのモデリングについて説明するようだ。

2013年12月9〜11日に米国ワシントンD.C.で開催される半導体素子の国際学会「IEDM 2013」の事前プログラムが発表された。これによると、最先端のCMOSプラットフォーム関連の「Session 9」が目玉の1つとなりそうだ。

Session 9では、TSMCが、同社の16nmプロセスのFinFET CMOSに関する論文の発表を行う。それに続き、14nm世代のFDSOI(Fully Depeleted Silicon-on-Insulator)プロセスに関する論文も発表する予定だという。FinFETに関する論文の著者は、全員がTSMCから参加しているが、FDSOIの論文の著者は、STMicroelectronicsとSoitec、欧州の研究機関であるLETI、IBM、GLOBALFOUNDRIES、ルネサス エレクトロニクスなどから参加しているようだ。

IEDMは、毎年12月上旬に開催される、エレクトロニクス分野において最も重要なイベントの1つだ。電子機器分野における学術研究と企業による研究開発とを橋渡しする役割を担っている。IEDM 2013の会場は、米国ワシントンD.C.のワシントンヒルトンホテル(Washington Hilton Hotel)である。

TSMCは、16nm FinFET/14nm FDSOI技術を発表

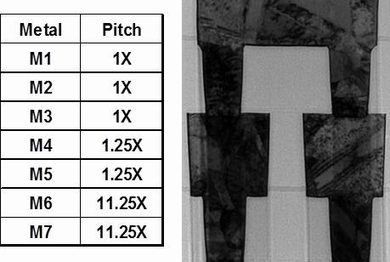

TSMCは近々、20nmプロセスを適用した回路の量産を開始する予定だ。また、16nm世代のFinFETプロセス開発についても、既に情報を公開している。TSMCの論文の著者は、モバイル/コンピューティングアプリケーション向けに最適化された16nm FinFETプロセスについて発表を行う予定だという。

論文の要約内容によると、16nm FinFETプロセスは、TSMCの28nm世代の高誘電率膜/金属ゲート(HKMG:High-k/Metal Gate)を適用したプレーナ型バルクCMOSプロセスと比べて、論理密度を2倍に高められるだけでなく、性能を35%以上向上させる(または、消費電力量を55%低減させる)ことも可能だという。さらに同社は、FDSOI関連の論文の発表において、14nm世代のプロセスを適用したゲート長20nmのデバイスに関する詳細を説明する。IEDM会場ではこの他にも、数多くのFDSOI関連の論文が発表される予定だ。

富士通セミコンの注目はメモリ技術

富士通セミコンダクターは、「Paper 9.6」の発表を行う予定だ。SuVoltaからライセンス供与を受けた「Deeply Depleted Channel(DDC)」技術を採用することによって55nm CMOS論理プロセスを向上させ、それを組み込み型不揮発性メモリに適用する手法について説明する。

Intelは9nm以降の技術を発表

Intelは、IEDMで発表予定の論文の中で、14nm以降の最先端プロセス技術の開発スケジュールについてまったく触れるつもりがないようだ。ただし同社のエンジニアは、Sesson 4でプレゼンテーションを行い、9nm世代以降のプロセス技術において、サブスレッショルド電圧(subthreshold voltage)で用いるIII-V族半導体材料を使った、トンネル電界効果トランジスタ(トンネルFET)のモデリングについて説明を行う予定だという。

IEDM 2013では、全33セッションにおいて215件のプレゼンテーションが行われる。最先端のCMOSプラットフォーム関連の論文は、これらの数多くの論文の中のほんの一部に過ぎない。メモリ関連の論文は、NAND型フラッシュメモリやReRAM(Resistive RAM:抵抗変化型メモリ)、CBRAM、FeRAM(Ferroelectric RAM:強誘電体メモリ)、PCM(Phase-Change Memory:相変化メモリ)など多岐にわたり、膨大な数に上る。エレクトロニクス市場の重要性は今後も増す一方であることから、IEDMでは、アナログ回路やMEMSセンサー、ディスプレイなどが重要視されていくだろう。また、バイオセンサーやバイオMEMSに向けた回路やプロセス技術のほか、エネルギハーベスティング技術やパワーデバイス、磁気デバイス技術、スピントロニクス技術なども対象分野となる見込みだ。

【翻訳:田中留美、編集:EE Times Japan】

関連キーワード

TSMC | 論文 | FinFET | SOI | 20nmプロセス | CMOS | 14nmプロセス | プロセス技術(エレクトロニクス) | Intel | FeRAM | ビジネスニュース(EE Times Japan) | 学会 | 富士通セミコンダクター | ルネサス エレクトロニクス | RRAM

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCの20nmプロセスは1種類、微細すぎて製品間の差をつけられず

TSMCの20nmプロセスは1種類、微細すぎて製品間の差をつけられず

28nmプロセスノードでは、高性能、低消費電力など4種類のプロセスを提供しているTSMCだが、20nmプロセスでは、1種類のみの提供になるという。線幅が小さすぎるために、複数の種類のプロセス(製品)を用意しても、性能面での差がほとんど出ないことが分かったからだとしている。 UMCがFinFETプロセスの実用化へ、TSMCを打ち負かすか

UMCがFinFETプロセスの実用化へ、TSMCを打ち負かすか

TSMCの後を追う二番手に甘んじてきたUMCだが、FinFETの製造開始においてはTSMCを打ち負かすことができるかもしれない。 20nmプロセス導入を急ぐTSMC、やはりAppleの次世代プロセッサを製造か

20nmプロセス導入を急ぐTSMC、やはりAppleの次世代プロセッサを製造か

TSMCが、20nmプロセスのCMOSチップの量産に向け、装置の導入を急いでいる。多くのアナリストが、この動きを「TSMCがApple向けに『A7』プロセッサを製造する」という予測に結び付けている。