BroadcomがARMベースの64ビットSoC投入へ、MIPSからシフト:プロセッサ/マイコン(2/2 ページ)

Broadcomは、MIPSアーキテクチャからARMアーキテクチャにシフトしていくようだ。同社の競合先も同じような計画を発表している。Broadcomは、まずは16nm FinFETプロセスを用いてカスタムコアを製造するという。

FreescaleもARMベースの通信向けプロセッサを発表

Freescaleも、2012年中旬に発表したアーキテクチャ「Layerscape」を採用した、同社初となるARMベースの通信向けプロセッサを発表する予定だ。これまで、Freescaleは、ハイエンド通信プロセッサ向けにはPowerPCコアを独自に設計していた。

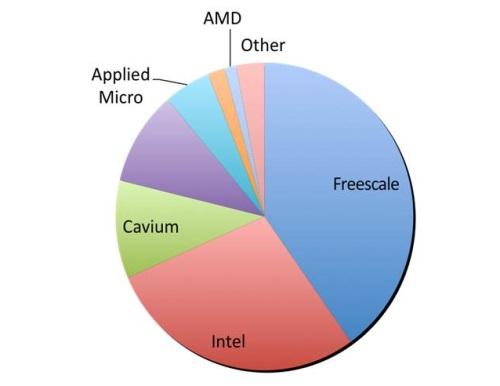

Gwennap氏は、「ただし、Freescaleは、2012年の通信プロセッサ市場のシェアランキングで、シェアを2ポイント落としている。その原因は、無線基地局の売上高の低迷にあった。一方、BroadcomはNetLogic Microsystemsの買収の結果、高い伸びを記録した。Intelも、2012年は順調な成長を遂げている」と解説している。同氏はまた、「通信プロセッサでは、Caviumは後れを取っている。同社の通信プロセッサ『Octeon II』は、市場投入が遅かった」と追加した。

IPコアベンダーの動き

Andes TechnologyとARM、ASOCS、Cadence Design Systems、CEVA、Imagination Technologies、Synopsysの7つのIPコアベンダーは、「Linley Processor Conference」(2013年10月16〜17日、米カリフォルニア州)で、新しい通信コアや既存コアの拡張を発表した。

CEVAは、第4世代「Ceva-XC」コアを発表した。従来および次世代のLTEシステムに向ける。同社は、「第4世代Ceva-XCは、無線インフラ向けの初の浮動小数点DSPだ」と主張している。最大40GFLOPS(ギガフロップス)/Wのエネルギ効率を実現し、消費電力は100mWと少ない。2×2 MIMOを採用したLTE向けピコセルに対応するという。

台湾に拠点を置くAndes Technologyは、「N1337」コアを投入している。40LP(Low Power)プロセスを適用し、1GHzを上回る高い周波数で動作する。消費電力は79mW/MHzで、1.88DMIPS/MHz、2.41Coremark/MHzの性能を実現する。

Andesはこれとは別に、9000個の追加ゲートを搭載するフラッシュベースのマイコンで、消費電力の低減と性能の向上を図る繰り返しコードシーケンスの処理技術「FlashFetch」技術を発表した。ホストCPUの処理速度の1/4で動作するフラッシュメモリの場合、フラッシュメモリの消費電力を半分に減らして、性能を54〜120%向上できるという。

ARMはLinley Processor Conferenceで、「Corelink」インターコネクトの拡張版を発表した。ARMベースのマルチコアSoCの製造に向ける。Gwennap氏は、Linley Processor Conferenceの基調講演で、「メモリのバンド幅とピン配列は依然として、通信SoCの主要なボトルネックになっている」と述べた。

Gwennap氏は、EE Timesのメール取材の中で、「最大の帯域幅が必要な場合、われわれはスタッキングによって対処しようと考える。従来のDDR設計をやめて、新しい高速インタフェースと組み合わせる場合は特にそうだ。しかし、価格の面から、コモディティメモリが引き続き圧倒的なシェアを占めることになるだろう」と述べている。

【翻訳:青山麻由子、滝本麻貴、編集:EE Times Japan】

関連キーワード

ARM | 通信 | Broadcom | ベンダー | MIPS | 64ビット | フリースケール・セミコンダクタ | DSP(Digital Signal Processor) | FinFET | PowerPC | サーバ | Imagination Technologies | ARM64 | プロセッサ/マイコン(エレクトロニクス)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelが“iPhone 5sのA7”と同じ64ビットSoC「Quark」を発表――マイコン市場を脅かすか?

Intelが“iPhone 5sのA7”と同じ64ビットSoC「Quark」を発表――マイコン市場を脅かすか?

Intelは、組み込み用SoC「Quark」を発表した。x86ベースの64ビットCPUを有し、従来の組み込み用SoC「Atom」に比べて、サイズは5分1、消費電力は10分の1だという。64ビットのアドレス空間の大きさを武器に、32ビットマイコン市場を脅かす可能性もある。 「1000億円でも当社は買えない」、DSPコアのCEVAが事業を説明

「1000億円でも当社は買えない」、DSPコアのCEVAが事業を説明

スマートフォンやタブレット端末の内部で無線通信やオーディオ、ビデオの処理を担うDSPコアで高い市場シェアを握るIPコアベンダーのCEVA。人員規模は世界で190名、売上高は6000万米ドル強だが、「1000億円あっても当社を買収することはできない」と主張する。 CPUコア業界に地殻変動、MIPSをImaginationが買収

CPUコア業界に地殻変動、MIPSをImaginationが買収

モバイル向けグラフィックスコアのImagination Technologiesが、CPUコアのMIPS Technologiesを買収する。買収金額は6000万米ドル。それと別にMIPSは、所有特許の8割超を、特許保持企業をメンバーとする業界コンソーシアムに3億5000万米ドルで売却するという。