SKハイニックス、次世代モバイル用DRAM「Wide I/O 2」を開発――20nmプロセス採用:メモリ/ストレージ技術

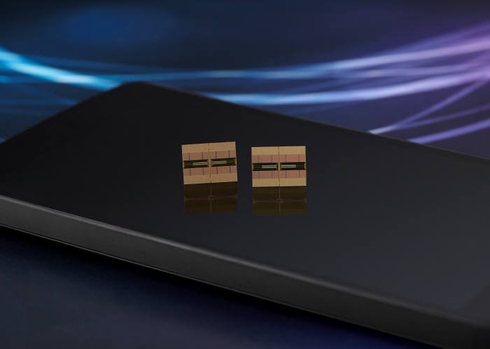

SKハイニックスは2014年9月、次世代モバイル用DRAM「Wide I/O 2」の開発に成功した。これは業界で初めて開発されたものとされ、これまで発表してきた超高速メモリ(HBM)と合わせて、既存のDDRシリーズで構成されたDRAM製品群を高性能メモリで広げることで、市場での地位を強固にするための試みとみられる。

消費電力25%削減

2014年9月、SKハイニックス(SK hynix)の代表であるパク・ソンウク氏は、「高性能モバイルDRAM『Wide I/O 2』を業界で初めて開発した」と明らかにした。

今回の製品は、20nmプロセスを適用して製造した8Gビットメモリで、I/Oのピン数がLP DDR4(Low Power DDR4)よりも16倍多い512個に達する。動作電圧は1.1VでLP DDR4と同じだが、電流効率を高めて電力消費を25%ほど減らした。

モバイルDRAMの中でもデータ処理速度が最も速い。LP DDR4は動作速度3200Mビット/秒で、データ処理速度が12.8Gバイト/秒だが、「Wide I/O 2」は動作速度800Mビット/秒で、データ処理速度は51.2Gバイト/秒に至る。動作速度は遅いが入出力のピン数が多く、1秒当たりのデータ処理量はLP DDR4の4倍にもなる。これまでの「Wide I/O 1」世代に比べても、データ処理速度は4倍ほど速くなった。

モバイル市場を狙う

高性能DRAMに対する需要が増加する中、SKハイニックスは既存のDDRシリーズで構成された DRAM製品群を高性能メモリによって広げている。「Wide I/O 2」ではモバイル市場を、2013年末と2014年4月にそれぞれ開発したHBMと128GバイトDDR4モジュールではサーバ用市場を狙う。

SKハイニックスは2013年末、シリコン貫通電極(TSV)技術を活用したHBMを開発した。20nmクラスプロセス採用DRAMを4段積層する技術を、量産レベルまでこぎつけた。I/O数は1024個で、動作電圧1.2V、動作速度1Gビット/秒で128Gバイト/秒のデータを処理することができる。ハイエンドグラフィック市場を皮切りに、今後ネットワーク、スーパコンピュータ、サーバ市場などに打って出る予定だ。

2013年4月、世界で初めて開発された20nmクラスプロセス採用8GビットDDR4モジュールにもTSV技術を適用し、既存のDDRモジュール最大容量64Gバイトの2倍である128Gバイトを実現した。この製品もサーバ市場をターゲットにし、2015年上半期には本格的な量産体制に入る予定だ。

SKハイニックスは、「Wide I/O」で高性能モバイルDRAM市場の攻略を強化するつもりだ。現在「Wide I/O 2」は、主要なシステム・オン・チップ(SoC)企業にサンプルとして供給されている。量産の目標時期の目安としては2015年下半期で、市場にはこの顧客企業のSoCとともにシステム・イン・パッケージ(SiP)の形で供給される。TSVも適用可能だ。

モバイルDRAMで主導権を

SKハイニックス モバイル開発本部長のキム・ジングク氏は、「『Wide I/O 2』で、高性能モバイルDRAMに対する顧客の要求を満足させる」と言い、「今後も高性能・低電力製品を開発し、モバイルDRAM市場の技術主導権を確保して行く予定だ」とコメントした。

「Wide I/O」は次世代DRAMの一種で、I/Oの数を大幅に増やしてデータ処理速度を高めた製品だ。モバイル用DDRシリーズのI/O数が32個であるのに対し、「Wide I/O」は512個に達する。現在、JEDECでも、標準化を進めている。2011年には、サムスン電子が伝送速度12.8Gバイト/秒のモバイル用「Wide I/O」を発表している。

Copyright© Electronic Times Internet. All rights reserved.

【翻訳/編集:EE Times Japan】

関連キーワード

DRAM | 性能 | DDR4 | Hynix Semiconductor | 20nmプロセス | 次世代 | サーバ | シリコン | 企業 | サーバ市場 | コンピュータ | メモリ/ストレージ技術(エレクトロニクス) | 消費電力 | 目標 | ハイエンド | Hybrid Memory Cube | LPDDR | SiP(System in Package) | SoC(System On Chip) | 標準化 | ストレージ | 転送速度 | ネットワーク伝送

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

DRAM市場は安定の時期に、激しい需給変動は終わる

DRAM市場は安定の時期に、激しい需給変動は終わる

Samsung、SK hynix、Micron Technologyの3社でシェアのほとんどを占めるDRAM市場。PC以外からの需要も増えてきて、需要と供給の変動が激しい時期は終わり、安定した市場になりつつある。 DRAM各社のプロセスを比較、さらなる微細化は可能か

DRAM各社のプロセスを比較、さらなる微細化は可能か

DRAMは、幾度となく「微細化はもう限界」だと言われてきた。だが、メーカー各社は2Xnmや1Xnm世代のDRAMの実現に向けて試行錯誤を繰り返し、成果を出し始めているという。 次世代メモリ「HMC」の仕様バージョン1を公開

次世代メモリ「HMC」の仕様バージョン1を公開

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。