「日本の製造業を再び世界一に」、アナログ・グルが語る:アナログ設計(2/3 ページ)

極めて優秀なアナログ回路技術者で「アナログ・グル」と呼ばれる日米4人の技術者が一堂に集まり、設計者が知っておくべきアナログ回路の特性や基本的な設計手法などについて語った。

ホットループの面積を最小化

続いて、Linear TechnologyのPietkiewicz氏とDobkin氏が、アナログ回路を開発するにあたって、設計者が知っておくべきアナログ回路の特性や基本的な設計手法などについて語った。Pietkiewicz氏は、主なスイッチングレギュレータと、EMI(電磁妨害)の発生源となる「ホットループ」に関して、詳細に説明した。

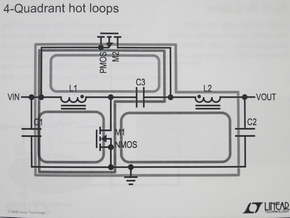

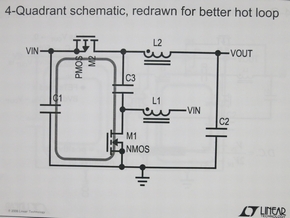

Pietkiewicz氏は、昇圧型、降圧型、SEPIC(Single Ended Primary Inductance Converter)、インバータ、絶縁型フライバック、4象限などのスイッチングレギュレータについて回路ブロックを示しながら、それぞれの特長と、ホットループについて解説した。スイッチングレギュレータにおいて、EMIの最も大きな発生源がホットループといわれている。このため、「ホットループの面積が最小になるようにしっかり回路設計しないと、電磁放射の問題で苦労する」と話す。電源回路に無線通信回路を実装しているわけではないが、ホットループ自体がアンテナの機能を持つことになるからだ。「無線アンテナを設計する技術と全く反対の技術を用いることで、EMIを抑えることができる」という。

4象限のホットループ。左が一般的な設計でC1、M2、C3、M1を含むルートがホットループとなる。右側は回路の最適化を図ったことでホットループの面積を小さくすることができた例 (クリックで拡大) 出典:リニアテクノロジー

4象限のホットループ。左が一般的な設計でC1、M2、C3、M1を含むルートがホットループとなる。右側は回路の最適化を図ったことでホットループの面積を小さくすることができた例 (クリックで拡大) 出典:リニアテクノロジーまた、表皮効果や近接効果、プリント基板上のビア設計などに関して、導体の形状や配線のレイアウト、グラウンドプレーン設計などにおいて注意すべき点についても触れた。会場では、受講者に対して表皮効果に関する問題も出された。「主要な新幹線で用いられている25kV漏えい同軸ケーブルの直径は?」。回答を導いた理由も含めて受講者と話し合った。

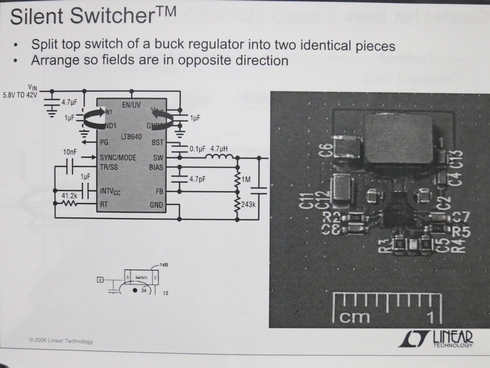

EMI特性を改善する最新の技術についてもその概要を紹介した。「サイレントスイッチャ(Silent Switcher)」と呼ぶ技術である。「レギュレータを2つに分けて、フィールドが逆になるようにすることで磁気ループがキャンセルされ、優れたEMI特性を達成した。CISPR25 Class 5のテストもかなり余裕をもって合格することができた」と述べた。

最後にPietkiewicz氏は、「EMI削減のために設計者は、まず部品の配置を行いホットループの面積を極小化すること。また、ビアでグラウンドプレーンを中断させないこと」と重ねて強調し、講演を締めくくった。

Copyright © ITmedia, Inc. All Rights Reserved.