ニュース

All Programmableデバイス向け開発環境、C/C++でFPGA回路設計も可能に:プログラマブルロジック FPGA(2/2 ページ)

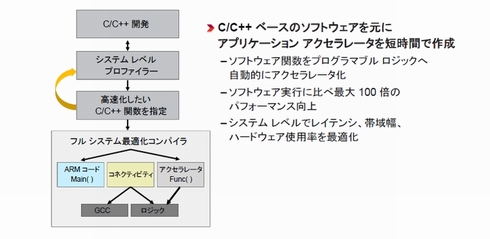

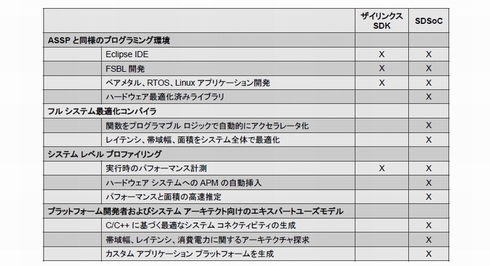

ザイリンクスは、All Programmable SoCおよびMPSoC向けの開発環境「SDSoC」を発表した。SDSoCを用いると、FPGAを設計した経験がほとんどない技術者でも、高速化したいC/C++関数を指定するだけで、自動的にハードウェア回路に置き換えることができる。

HDLで作成した最適化済みライブラリも活用可能

また、ザイリンクスやサードパーティーがHDLで作成した最適化済みライブラリ(IPブロック)も活用することができる。これらのライブラリはCコードで呼び出すことができるライブラリへと容易に変換することができ、これを再利用することで開発効率を高めることができる。さらに、ザイリンクスやサードパーティー製の開発プラットフォームを利用すれば、システムアーキテクチャの検討を行うための仕様変更なども短時間で行うことができる。

SDSoCは、これまでも提供されてきた、Zynq上で動作するソフトウェアとハードウェアの性能を測定するソフトウェアプロファイリング機能を拡張している。新たに追加されたのはシステム性能全体を短時間に推定する機能である。「システムレベルプロファイリング」と呼ぶこの機能は、ハードウェアで高速処理したい関数を指定することで、SDSoCがC/C++コードを分析して、ソフトウェアサイクル数、データ転送量、アプリケーション全体での速度向上率などを算出することができる。これにより、実行性能を計測しながら、最適なシステム構成を短時間で推定することができる。

SDSoCについては、既にアーリーアクセスプログラムを実施中で、アーリーアクセス版は同社の販売代理店より入手することが可能である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表

16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表

ザイリンクスは、16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリを発表した。従来の28nmプロセスFPGA/SoCに比べて、消費電力当たり2〜5倍のシステム性能を実現することが可能となる。 ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

Xilinx(ザイリンクス)は2014年11月、エンジニアリングサンプル(ES)出荷段階にある20nmプロセスを用いたFPGA「Virtex UltraScaleファミリ XCVU095」を使用した400Gビット イーサネットの動作デモを公開した。 ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス日本法人は、現行の主力28nmプロセス採用FPGAの受注が好調だという。同社社長を務めるサム・ローガン氏に好調の理由や、今後、投入を本格化させる20nmプロセス採用FPGA製品のビジネス展望などを聞いた。 ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。 ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスは2014年3月期通期業績を公表し、28nmプロセス採用製品の売り上げ伸長などから過去最高売上高を記録したと明かした。