ARMから見た7nm CMOS時代のCPU設計(2):福田昭のデバイス通信(13)(1/2 ページ)

前回、設計技術者とデバイス技術者の間には距離があることを説明した。CPUの設計者がデバイス技術者にする質問は常に同じだが、それに対するデバイス技術者の答えにはズレがあるのだ。今回は、そのズレについて説明したい。

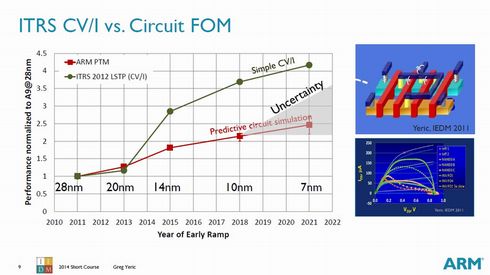

実際のCPU性能は、業界のロードマップ通りには向上しない

前回で説明した質問と回答を実際の設計に当てはめると、デバイス技術者の「回答」が「解答」になっていないことが分かる。最初の質問は「(1)設計ノードの進化によってCPUはどのくらい速くなるのか」であり、デバイス技術者の典型的な回答は「(1)ITRSロードマップのCV/Iを読め」だった。ここで「ITRSロードマップ」とは、半導体デバイス技術者が作成し、改訂してきた技術ロードマップであり、「CV/I」とは、nMOSトランジスタの遅延時間(CRの積で決まる時定数)に相当する。

ARMのCPUコア製品「ARM Cortex-A9」で、2012年版のITRSロードマップとARMが実際に設計したマクロセル(PTM:Program Flow Trace Macrocell)の性能(相対性能)を設計ノードごとに比較した。28nmノードでの性能を「1」とすると、次世代の20nmノードでは「1.2〜1.3」に性能が向上する。このノードでは、ITRSとARMで性能の差はほとんどない。ところがその次の14nmノードでは、ITRSでは性能が「3」近くにまで向上するのに対し、ARMのマクロセルは性能が「2」弱までしか向上しない。さらに先のノードでは、違いはさらに大きくなる。7nmノードではITRSの性能が4倍強に達するのに対し、ARMのマクロセルでは2.5倍にとどまってしまう。つまり、ITRSロードマップの通りには、性能は向上しない。性能の向上はロードマップよりも緩やかになる。

Copyright © ITmedia, Inc. All Rights Reserved.