ARMから見た7nm CMOS時代のCPU設計(2):福田昭のデバイス通信(13)(2/2 ページ)

前回、設計技術者とデバイス技術者の間には距離があることを説明した。CPUの設計者がデバイス技術者にする質問は常に同じだが、それに対するデバイス技術者の答えにはズレがあるのだ。今回は、そのズレについて説明したい。

消費電力密度は増えるが、消費電力は増やせない

2番目の質問についても同様である。質問は「(2)CPUの消費電力はどのように変化するのか」であり、デバイス技術者の回答は「トランジスタの電力消費はCV2F(容量×電圧の2乗×動作周波数)」だった。そもそもCPU全体の消費電力を問うているのに対し、回答がトランジスタレベルというのではズレがある。

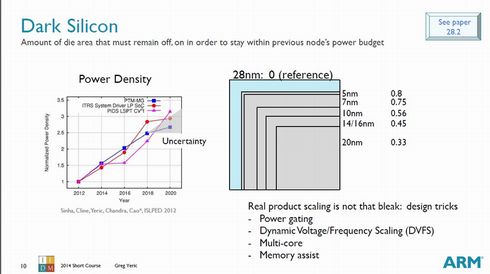

ズレを承知の上で消費電力密度(相対値)を予測すると、2012年に「1」だった消費電力密度は、2020年にはおよそ「3」に達する。しかし放熱の条件やバッテリ容量の制約などにより、シリコンダイ全体の消費電力は、3倍には増やせない。そこでシリコンダイの中で電源をオフにするエリア(ダークシリコン)を増やし、消費電力の増大を抑制する。

ダークシリコンは、シリコンダイの平均的な消費電力を維持するためには、不可欠の存在である。シリコンダイ面積に占めるダークシリコンの割合は、設計ノードの進化とともに増加する傾向を示す。例えば28nmノードではダークシリコンの比率はゼロだったと仮定しよう。これが20nmノードでは33%、14/16nmノードでは45%、10nmノードでは56%と、ダークシリコンの割合は急速に増加していく。7nmノードでは、ダークシリコンの比率は75%に達する。実にシリコンダイの3/4が利用されないという状態になってしまう。

ただし、実際のCPUコア設計は、これほど悲観的なものではない。いくつかの設計上の工夫が盛り込まれるからだ。負荷の増減に応じて電源電圧や動作周波数などを動的に変化させたり(DVFS技術)、マルチコア化して動作周波数を抑えたり、メモリ技術の改善によって電力消費を低減したりする。

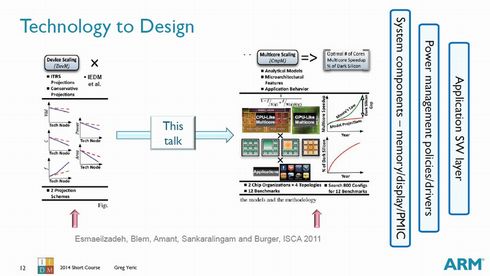

トランジスタ性能をシリコンダイに落とし込む

ARMの講演は、ここからが本論である。それはトランジスタの性能トレンドを把握しつつ、その性能を維持しながら、SoC(System on a Chip)のシリコンダイに落とし込むことだ。トランジスタレベルのデバイス設計と、論理レベルの回路設計を結びつける作業である。次回からは、その詳細を述べていく。

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

サーバ用CPU市場に挑むAMDとARMの思惑――ゲーム機の成功モデルをサーバでも

サーバ用CPU市場に挑むAMDとARMの思惑――ゲーム機の成功モデルをサーバでも

AMDは、ARMの64ビットコアを採用したサーバ向けCPU「Seattle(開発コードネーム)」を、2014年第2四半期にサンプル出荷することを明らかにした。AMDは、ARMサーバ市場でシェアを伸ばすために、同社がゲーム機市場で成功したときのモデルを持ち込もうとしている。すなわち、カスタムSoCの開発だ。Seattleを汎用品として市場に投入したあとは、そうしたカスタムSoCの開発を進める予定としている。 終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

終えん間近のムーアの法則、“ポストCMOS”の技術を模索へ

米国で開催されたシンポジウム「IEEE Technology Time Machine(TTM)2014」では、“ポストCMOS”の技術について議論が交わされた。注目されているのは、量子コンピュータ、ビッグデータ、カーボンナノチューブ、人間の脳(シナプス)をまねた技術などである。 ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査

ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査

オランダのKPMGが半導体業界のビジネスリーダーを対象に調査したところ、「ムーアの法則の有用性は存続する」と予想しているのは、回答者の1/4で、半数以上が「22nmプロセス以降では、ムーアの法則の存続は難しい」と考えていることが分かった。 ARM社のデュアルコアCortex-A9、低消費電力版でも性能はAtomを上回る

ARM社のデュアルコアCortex-A9、低消費電力版でも性能はAtomを上回る

デュアルコアCortex-A9は、2種類のハードマクロの形で提供される。用途に合わせて処理性能を重視した版と、消費電力を重視した版を選択できる。2GHz動作時(1万DMIPS)の消費電力は1.9W、1GHz動作時(4000DMIPS)の消費電力は0.5Wだ。 「Cortex-A15」の開発事例を富士通セミが明かす、動作周波数は2GHz以上に

「Cortex-A15」の開発事例を富士通セミが明かす、動作周波数は2GHz以上に

ARMの最先端プロセッサコア「Cortex-A15」を搭載するASICを富士通セミコンダクターが開発中である。TSMCの28nm HPMプロセスで製造しており、動作周波数は2GHz以上になる見込みだ。