次世代3次元SoCは、TSVを使わない――Qualcomm:プロセス技術(2/2 ページ)

Qualcommは、米国で開催された「International Symposium on Physical Design(ISPD)」で、同社の3次元SoCの技術動向について語った。TSV(シリコン貫通ビア)を使わずに積層することで、小型化と歩留まりの向上を実現したいという。

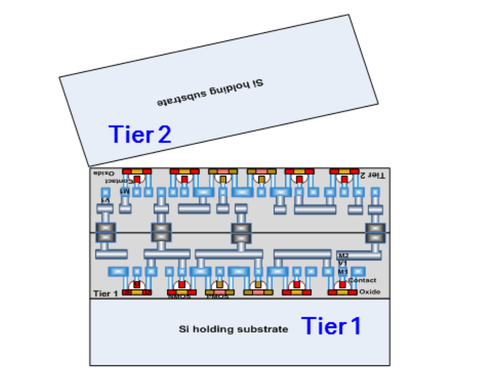

F2BとF2Fを組み合わせる

方法としてはF2Bの方が簡単だ。F2Bは精密な接合が不要で、第1層の上部にシリコン薄膜を形成して、従来のビア技術を使って第2層を構築する。だが、下位層は1200℃もの高温で製造される場合が多いが、第2層は銅インターコネクトが溶けないように温度を1085℃までに制限しなければならない。

この課題を解決するために、Qualcommはインターコネクトにタングステンを使った。タングステンの融点は3422℃である。

もう1つの対策は、上位層に温度制限(例えば625℃など)を設けることだ。だが、この手法だと、第2層のトランジスタ性能がpチャンネルMOSFETで27.8%、nチャンネルMOSFETでは16.2%低下してしまう。現在のF2B技術では性能面で37%、処理能力で41%を犠牲にすることになり、理想的な3Dチップを作製することはできない。

一方でF2Fでは、銅インターコネクトを使うことができ、トランジスタ性能もそこまで低下しない。だが、よりサイズの大きいビアが必要になり、精密な接合ができなくなるというデメリットがある。

Qualcommは、F2BとF2Fを組み合わせれば、無限に積層できる3DV SoCを製造できると考えた。

Arabi氏によると、この方法では、コストがかかる最先端の製造プロセスは下位層だけに使えばよいという。例えば、CPUやGPUを集積する下位層は10nm〜14nmプロセスで製造し、機能的にCPU/GPUなどほど重要ではないチップは、コストの安い、より成熟したプロセス(28nmなど)で作ることができるとしている。なおArabi氏は、最も歩留まりが高い3DV SoCは2層構成で、3層構成になるのは、RFチップなどを上位層にさらに積層する場合などだという。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

中国がQualcommに独禁法違反判決、特許使用料はどうなる?

中国がQualcommに独禁法違反判決、特許使用料はどうなる?

中国がQualcommに対し、独占禁止法に違反したとして罰金の支払いを命じた。同時に、Qualcommの特許使用料率も引き下げている。 カーボンナノチューブ素子のICチップ、 “せっけん”と“トレンチ”で実用へ前進

カーボンナノチューブ素子のICチップ、 “せっけん”と“トレンチ”で実用へ前進

IBMの研究チームは、現行の標準的な半導体プロセスを使って、カーボンナノチューブを用いたトランジスタ素子を1枚のチップ上に1万個以上作り込むことに成功したと発表した。こうした成果は世界初であり、シリコンの次を担う半導体材料として期待されるカーボンナノチューブ・ベースの集積回路(IC)の商用化を大きく進展させると主張している。 エッチング装置やテスト装置、3次元IC時代に備える

エッチング装置やテスト装置、3次元IC時代に備える

FinFETなどの3次元ICは、半導体業界のトレンドの1つだ。セミコン・ジャパン 2013では、そうした流れをくんで開発されたエッチング装置やテスト装置が紹介されていた。 3Dチップ開発、メーカーの動きは?

3Dチップ開発、メーカーの動きは?

3次元積層技術を用いたチップ(3Dチップ)の開発動向に注目が集まっている。こう着状態にも見える3Dチップの開発だが、メーカーは着実に前進しているようだ。 サムスンとGLOBALFOUNDRIESが14nmチップで提携、2014年内に製造開始へ

サムスンとGLOBALFOUNDRIESが14nmチップで提携、2014年内に製造開始へ

サムスン電子(Samsung Electronics)とGLOBALFOUNDRIESは、同じ14nmプロセスを使用してチップを製造することで合意した。サムスンは2014年内に、GLOBALFOUNDRIESは2015年前半にも量産を開始する予定だとしている。