連載

ARMから見た7nm CMOS時代のCPU設計(9)〜CPUの性能向上に不可欠な設計の「手戻り」:福田昭のデバイス通信(20)(2/2 ページ)

今回は、LSI設計作業の所要時間について解説する。設計の各工程ではイタレーション、つまり「手戻り」と呼ばれる修正作業が発生する。CPUの動作周波数を上げるためには、膨大な数の手戻りが行われている。

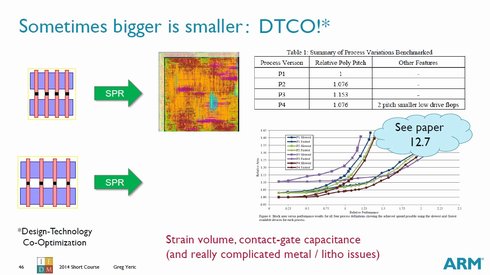

ゲートピッチは短ければよいとは限らない

設計の修正作業を繰り返すことによるフロアプランの変化を見ていくと、動作周波数の増大に伴ってシリコン面積が増大していることが分かる。動作周波数が高いフロアプランは、シリコン面積が明らかに大きい。一般的には、シリコン面積が大きくなると配線長が伸び、負荷容量が増加するので動作周波数はあまり伸びないとされている。しかし実際にはしばしば、シリコン面積が大きい方が動作周波数が高いことがある。

さらに興味深いのは、基本単位であるゲートピッチの扱いだ。ゲートピッチは短ければよいとは限らない。ゲートピッチを長めに確保した方が、CPUの動作周波数は高くなり、しかもシリコン面積が小さくなることがある。

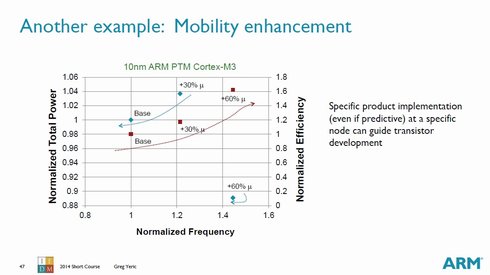

キャリア移動度の向上で性能を高める

動作周波数の向上には、トランジスタのキャリア移動度の向上も大きく影響する。ひずみシリコン技術といったトランジスタのキャリア移動度を上げる手法が最先端のトランジスタには組み込まれている。

キャリア移動度の変化とイタレーションによって同じ動作周波数でも、消費電力を大幅に下げることができる。例えばキャリア移動度が標準値よりも30%高いときに動作周波数は1.2倍に向上するものの、消費電力も4%ほど増加する。これをイタレーションにより、増分をゼロにする。移動度を60%を上げることで動作周波数を1.4倍強に高め、消費電力を10%ほど下げられることを、講演では見せていた。

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

富士通とパナソニックのシステムLSI事業統合に関する“6つの疑問”

富士通とパナソニックのシステムLSI事業統合に関する“6つの疑問”

富士通とパナソニックは、2014年内に両社のシステムLSI事業を統合して新会社を設立する。ただ、この新会社は、どのようなシステムLSIをどのように製造し、どうやって利益を上げていくか、あまり明らかにされていない。そこで両社に“6つの疑問”を投げかけた。 塗って乾かすだけの有機半導体でRFIDタグの動作に成功

塗って乾かすだけの有機半導体でRFIDタグの動作に成功

東京大学などのグループは、印刷で製造可能な高性能有機薄膜トランジスタ回路を開発し、電子マネーカードなどで用いられる商用周波数(13.56MHz)での個体識別信号の伝送に「世界で初めて成功した」(東京大学)と発表した。 動き出すSiCパワー半導体、省エネルギーの切り札へ

動き出すSiCパワー半導体、省エネルギーの切り札へ

CO2の25%削減目標やこれまでにない規模の太陽光発電の導入、米国や中国を中心に急速に立ち上がり始めたスマートグリッドなど、従来とは異なる省エネルギー対策が必要となってきた。いずれも電力の変換技術が必要不可欠だ。ところが、電力変換用に用いられてきたSi(シリコン)パワー半導体の性能はこれ以上伸びそうにない。このような状況で脚光を浴びているのが、実力でSiを大きく上回るSiC(炭化ケイ素)やGaN(窒化ガリウム)を用いたパワー半導体である。例えば、SiCをインバーターに用いたときの損失は、従来のSi素子を用いたときに比べて1/100になる可能性がある。 IGZOを超える「有機半導体」、分子設計からトランジスタまで日本発の新技術

IGZOを超える「有機半導体」、分子設計からトランジスタまで日本発の新技術

シリコンでは実現できない新しい機能性有機材料を東京工業大学の半那純一教授、飯野裕明准教授のグループが開発した。大きく3つの成果があるという。低分子系有機トランジスタ材料で耐熱性と成膜性を実現したこと、多結晶膜で高い移動度を得たこと、2分子層構造を利用して高移動度が実現できたことだ。 SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの量産採用に向けた課題の1つとして挙げられているのが、酸化シリコンを用いたゲート絶縁膜に起因する動作時の信頼性の低さだ。大阪大学と京都大学、ローム、東京エレクトロンは、AlON(アルミニウム酸窒化物)を用いたゲート絶縁膜によって、SiC-MOSFETの信頼性を高める技術を開発した。