連載

ARMから見た7nm CMOS時代のCPU設計(15)〜オンチップSRAMのスケーリング問題:福田昭のデバイス通信(26)(1/2 ページ)

今回は、SRAMの微細化について触れる。16/14nm世代までは微細化が順調に進んできたが、数多くの課題が存在する。周辺回路を縮小しにくいことが、その1つとして挙げられる。

CPUに不可欠なキャッシュメモリの内蔵

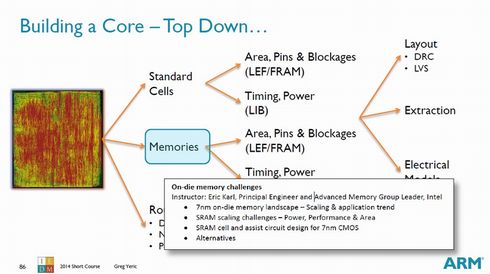

CPU設計ではロジック設計のほかに、メモリ設計が存在する。具体的には、キャッシュメモリやタグメモリなどのオンチップメモリ(内蔵メモリ)の設計である。CPUのオンチップメモリ技術には過去から現在までずっと、主にSRAM技術が使われてきた。SRAM技術はロジックとプロセスの互換性があり、なおかつ、きわめて高速にデータを読み書き可能であるからだ。

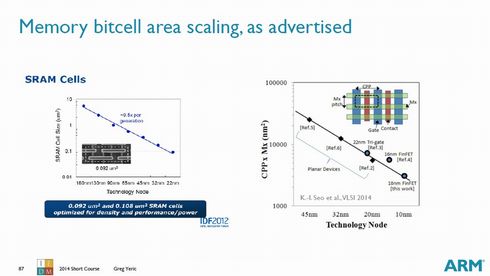

SRAMの微細化(スケーリング)は、最新世代である16/14nm世代までは、ほぼ順調に進んできた。Intelが公表したデータによると、SRAMセルのシリコン面積は、微細加工の世代が進むごとに約2分の1に小さくなってきた。このトレンドは180nm世代から130nm世代、90nm世代、65nm世代、45nm世代、32nm世代、22nm世代と少なくとも6世代もの間、維持されてきた。また別の研究データによると、ゲートピッチ×メタルピッチ(第1層金属配線のピッチ)で表記される区画の面積は、45nm世代から、32nm世代、22nm世代、16nm世代、10nm世代まで、ほぼ一定のペースで縮小できている。

SRAMセルのトランジスタは32nm世代まではロジックと同様のプレーナ型FETだった。22nm世代以降はロジックと同様に、FinFETの導入が始まっている。ただしFinFETが本格的に導入されるのは、16/14nm世代からになるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.