ARMから見た7nm CMOS時代のCPU設計(15)〜オンチップSRAMのスケーリング問題:福田昭のデバイス通信(26)(2/2 ページ)

今回は、SRAMの微細化について触れる。16/14nm世代までは微細化が順調に進んできたが、数多くの課題が存在する。周辺回路を縮小しにくいことが、その1つとして挙げられる。

周辺回路が縮小しづらい

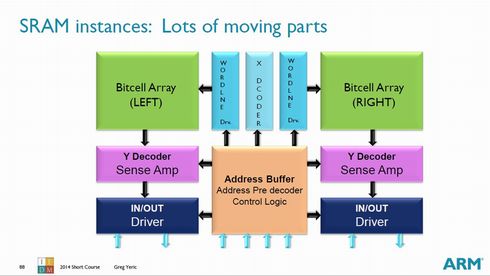

SRAMを構成する主要な部分はメモリセルをマトリクス状に配置したメモリセルアレイである。1個〜4個程度のブロックに分割されたメモリセルアレイは、メモリセルが小さくなることでそのままセルアレイ全体が縮小される。言い換えると、比較的単純に縮小できる。ただしSRAMの構成要素はメモリセルアレイだけではない。周辺回路がある。

周辺回路には入出力バッファ、行デコーダ(Xデコーダ)、ワード線ドライバ、列デコーダ(Yデコーダ)、センスアンプなどがある。これらの周辺回路の縮小は、メモリセルアレイほどには単純には進まない。例えばメモリセルアレイのゲート配線を駆動するワード線ドライバは、トランジスタを単純に縮小すると電流駆動能力が低下する。オンチップキャッシュの記憶容量が前の世代のシリコンダイと等しければ問題は少ないものの、実際には世代交代に伴ってオンチップキャッシュの記憶容量を拡大することが多い。するとワード線の配線抵抗と配線容量が増加し、単純な縮小ではワード線の電流駆動能力が不足する。対策としてはワード線ドライバのトランジスタを大きくする、ワード線を分割してプリドライバを挿入する、などがある。ただしいずれも、シリコン面積の拡大を招く。

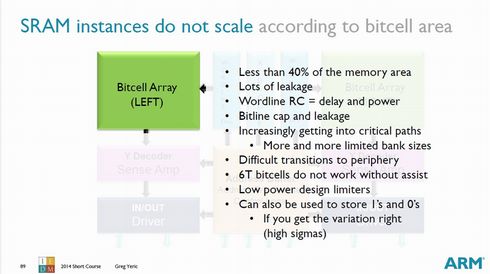

そのほかにも課題は数多く存在する。ワード線抵抗とワード線容量の問題は先に述べた通りだ。ビット線の容量とリーク電流の増加も問題になる。消費電流の制約条件を満たすことが難しくなる。また電源電圧の低下により、6個のトランジスタで構成したメモリセルでは、アシストなしでは動作しなくなるという懸念もある。メモリセルアレイではバンクの大きさに対する制限が厳しくなる。クリティカルパスの増加を抑制するためである。ばらつきの増大も心配だ。

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

不揮発性パワーゲーティング、メニーコアプロセッサの待機電力削減に威力

不揮発性パワーゲーティング、メニーコアプロセッサの待機電力削減に威力

東京工業大学(東工大)像情報工学研究所の菅原聡准教授らの研究グループと神奈川科学技術アカデミー(KAST)は、不揮発性パワーゲーティング(NVPG)がメニーコアのプロセッサやSoCの待機時電力削減に極めて有効なアーキテクチャであることを実証した。 ニッチ用途の域を出ないMRAM、普及の鍵はコストと記録密度

ニッチ用途の域を出ないMRAM、普及の鍵はコストと記録密度

幅広い用途でDRAMやSRAMの置き換えになると予想されているMRAM(磁気抵抗メモリ)。産業用途を中心に採用が進んでいるが、普及が加速するにはまだ時間が必要なようだ。 メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目

メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目

今回は、大容量化と高速化が進む半導体メモリに焦点を当てる。メモリ市場の二大勢力となっているDRAMとNANDフラッシュメモリについての講演が多い。15nmプロセスを採用したNANDフラッシュメモリや、車載マイコン向けフラッシュメモリ技術、次世代のDRAMインタフェースなどに関する発表がある。 「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

ルネサス エレクトロニクスは、16nm FinFETプロセスを用いてSRAMを試作したと発表した。プレーナ型MOSFETを使う場合に比べて低い動作電圧で高速読み出しに成功しているが、一方でFinFETと、微細化プロセスを用いたことによる課題も増えている。