IBMが7nm試作チップを発表、Intelに迫る勢い:EUVとSiGeチャネルで(3/3 ページ)

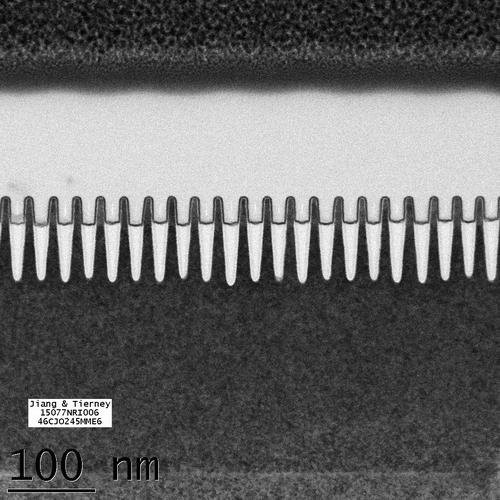

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。

量産までには長い道のり

Khare氏は、「EUVは非常に難しい技術で、7nmプロセスでの製造を成功させるには、多くの材料の変更や最適化が必要だった。だが、IBMには半導体技術で画期的な成果を上げてきた実績がある。例えば、シングルセルDRAMや化学増幅フォトレジスト、銅インターコネクト、SOI(シリコン・オン・インシュレータ)、歪みエンジニアリング、マルチコアプロセッサ、液浸リソグラフィ、high-k(高誘電率ゲート絶縁膜)、組み込みDRAM、3次元チップ積層などだ。当社は2014年に、今後5年間で30億米ドルの投資を行うと発表したが、今回の7nm試作チップは、進化の幕開けにすぎないだろう」と述べている。

Endpoint Technologies AssociatesのプレジデントであるRoger Kay氏は、EE Timesに対し、「7nm試作チップは素晴らしい成果だ。ただ、量産までには長い道のりが待っているだろう」と述べている。「Intelは7nmプロセスの開発について強い自信を示してきたが、ここ最近はおとなしく、7nmプロセスではIBMの方が先行しているようにも見える。IBMは、各メーカーが苦戦しているEUV技術を(今回の試作チップに)使用し、SiGeチャネルを採用したことも、注目に値する発表だ。IBMの計画が予定通りに進めば、2016年には10nmチップのサンプルが登場するだろう。Intelの10nmチップのサンプルも同じころに出てくると思われる」(同氏)。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か

Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か

Intelは10年近くにわたり、量子井戸電界効果トランジスタ(QWFET)の研究を進めてきた。ある半導体アナリストは、Intelの10nmチップは、III-V族半導体、具体的にはInGaAs(インジウム・ガリウム・ヒ素)とGe(ゲルマニウム)を用いたQWFETになると予測している。 ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

TSMCが、ASMLにEUV(極端紫外線)露光装置2台を発注していたことが明らかになった。TSMCは、EUVリソグラフィによって7nmプロセスの実現を目指すとみられている。2015年末には7nmプロセスを適用したチップのリスク生産が開始される可能性がある。 IBMのEUV試験結果に疑問の声、インテルは「EUVなしで7nm実現を模索」

IBMのEUV試験結果に疑問の声、インテルは「EUVなしで7nm実現を模索」

IBMが2014年7月に発表した、EUV(極端紫外線)リソグラフィスキャナーに関する最新テストの結果を、いぶかしむ業界関係者が少なくない。今回のIBMのテスト結果は、EUVの実用化に向けてどのような意味を持つのだろうか。 IBMがEUVのスループットで記録更新、1日637ウエハー

IBMがEUVのスループットで記録更新、1日637ウエハー

IBMは2014年7月、ASML製の最新のEUV(極端紫外線)リソグラフィシステムの試験初日に「予想以上の結果を得た」と発表した。スキャナー「NXE3300B」に44Wの光源を用いて、安定した速度(34ウエハー/時)を保って、24時間で637枚のウエハーを作り出したという。