Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か:プロセス技術

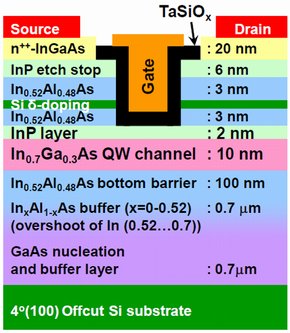

Intelは10年近くにわたり、量子井戸電界効果トランジスタ(QWFET)の研究を進めてきた。ある半導体アナリストは、Intelの10nmチップは、III-V族半導体、具体的にはInGaAs(インジウム・ガリウム・ヒ素)とGe(ゲルマニウム)を用いたQWFETになると予測している。

ある半導体アナリストが、Intelが次の2世代で用いるプロセス技術について大胆かつ詳細な予測を立てている。この予測が正しければ、Intelは業界で再び一歩先を行くようになるだろう。

そのアナリスト、David Kanter氏は、自身のWebサイト「Real World Technologies」に投稿した記事の中で、Intelは10nmプロセス以降、QWFET(Quantum-Well FET:量子井戸FET)を用いるようになると述べた。この新たなトランジスタ構造では、2つの新素材が用いられるようになる。具体的には、n型トランジスタ向けにInGaAs(インジウム・ガリウム・ヒ素)、p型トランジスタ向けにはひずみゲルマニウム(Ge)が用いられるようになるという。

2016年に10nmチップが登場する可能性も

Kanter氏の予測が正しければ、Intelは早ければ2016年に、動作電圧が他社に比べて200mV低い(1Vから0.8Vに低減)トランジスタを10nmプロセスで製造できる可能性がある。Kanter氏は、他のチップメーカーは7nmプロセスまでIntelの技術に追い付くことができず、少なくとも2年の後れを取ると見ている。

Kanter氏は、自身の予測の信頼度を80〜90%とした上で、Intelが10nmプロセスに関する計画を明らかにするのは1年以上先になると述べた。

Kanter氏の見解は、Intelが主に「International Electron Devices Meeting(IEDM)」で発表した24本の論文に基づいている。さらに同氏は、チップの製造に関連するIntelの特許についても分析したという。

Kanter氏はEE Timesに対し、「私が得た情報は全て、IntelがQWFETを採用するという方向性を指し示していた。ただし、重要なのはQWFETを用いるのかどうかという点ではなく、それを10nmで採用するのか、7nmで採用するのかという点である」と語った。

Kanter氏は「チャネルで化合物半導体を用いる研究を進めているのはIntelだけではない。だが、Intelと同等レベルまで研究を進めているメーカーは他にはないだろう。Intelのゲルマニウムに関する論文や特許はそれほど多くないが、同社はゲルマニウム関連の技術をよく理解しているように見える」と述べた。Kanter氏は、Intelが純ゲルマニウムを使うと見込んでいる。

Kanter氏は自身の記事を公開する前にIntelに提供したが、それについてのコメントは拒否している。

【翻訳:青山麻由子、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- 【IEDM 2010】III-V族材料使う量子井戸FET、インテルが改善進める

ムーアの法則はまだ終わらない、存続の鍵はGaAs材料

ムーアの法則はまだ終わらない、存続の鍵はGaAs材料

POET Technologiesは、ムーアの法則を続ける鍵になる材料として、GaAs(ガリウムヒ素)を挙げている。高いスイッチング周波数を実現できるだけでなく、光回路と論理回路を同一チップに集積できるという利点もある。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 トレンチ構造を用いたSiC-MOSFETを製品化――ロームが6月量産

トレンチ構造を用いたSiC-MOSFETを製品化――ロームが6月量産

ロームは2015年4月23日、トレンチ構造を用いたSiC(炭化ケイ素)によるMOSFET(以下、SiC-MOSFET)を開発し、2015年6月から量産すると発表した。 “ポストシリコン”狙うカーボンデバイス、性能も製造性も着実に向上

“ポストシリコン”狙うカーボンデバイス、性能も製造性も着実に向上

現在、半導体材料の圧倒的な主流はシリコンである。しかし、材料特性がシリコンとは大幅に異なる点を利用して新しい機能のデバイスを実現しようとする取り組みも進んでいる。先週ワシントンD.C.で開催された半導体デバイス技術に関する世界最大の国際会議「IEDM 2011」から、最新の研究成果をリポートする。