連載

ARMから見た7nm CMOS時代のCPU設計(20)〜まとめ:CPU設計の将来像:福田昭のデバイス通信(31)(2/3 ページ)

シリーズ最終回となる今回は、これまでの内容をまとめてみよう。トランジスタの将来像から、消費電力と性能のバランスの取り方、微細化(スケーリング)の余地の拡大まで、ひと通り振り返る。

消費電力とコストの制約を満たしつつ性能を最大化する

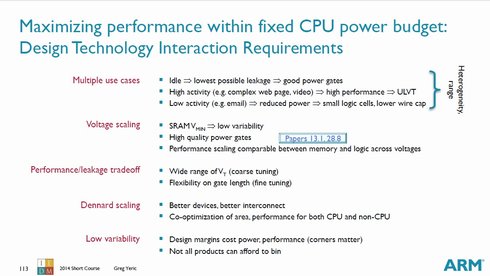

そしてCPU設計の将来像を展望した。CPU設計では前提として、消費電力とコストの上限が定められている。これらの上限を順守した上で、CPUの処理性能を最大化しなければならない。しかし常に最大性能を出せる状態にしておくことは、得策ではない。待機時消費電力が増大したり、シリコン面積が増加したりするからだ。

今後のCPU設計では、複数の使われ方、すなわち負荷の違いに応じて動作するハードウェアを適切に変更することが求められる。重い負荷ではしきい値の低いトランジスタを動かし、軽い負荷では小さく高密度なロジックを動かす。アイドル状態では、不要な電源ドメインの電源を遮断する。

システムを想定すると、電力と性能とシリコン面積とコスト、いわゆる「PPAC(Power, Performance, Area, Cost)」のバランスを考慮しなければならない。IEDMに代表される国際学会で公表された次世代トランジスタのパラメータを利用して、次世代システムのPPA(電力と性能とシリコン面積)を推測することが重要である。

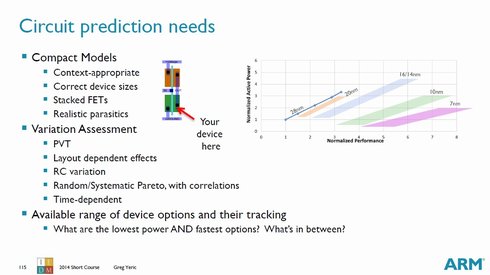

次世代のシステムを予測するためには、次世代の回路も予測しなければならない。回路の動作速度が最大になるパラメータと、回路の消費電力が最小になるパラメータの間の領域を、あらかじめ把握しておく必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.