連載

ARMから見た7nm CMOS時代のCPU設計(20)〜まとめ:CPU設計の将来像:福田昭のデバイス通信(31)(3/3 ページ)

シリーズ最終回となる今回は、これまでの内容をまとめてみよう。トランジスタの将来像から、消費電力と性能のバランスの取り方、微細化(スケーリング)の余地の拡大まで、ひと通り振り返る。

微細化(スケーリング)の余地を拡大する

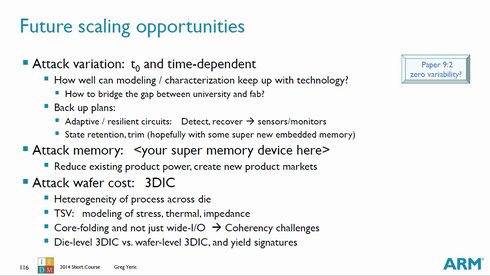

微細化(スケーリング)の余地を拡大していく努力も欠かせない。まず、増大するばらつきに対処する。ばらつきを抑えるためには、ばらつきのモデリングが不可欠である。良好なモデルによってばらつきの特性を把握し、対処手法を見つける。

それから、メモリ技術の革新がきわめて重要になる。現在のメモリを超える、新しいメモリ(次世代不揮発性大容量メモリ)の開発に大きな期待がかかる。

そして3次元IC技術は今後、ますます重要になるだろう。異なるプロセス技術で製造された複数のシリコンダイを積層した半導体製品が増加していく。シングルダイに集積するよりも、製造コストが安価であることが強みだ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

IBMがIII-V族化合物半導体を使ったFinFETの開発成果を積極的に発表している。IBMは、局所横方向エピタキシャル成長(CELO)技術により、シリコンおよびSOI基板の両方に、通常のCMOSプロセスで、InGaAsのFinFETを形成したと発表した。 GLOBALFOUNDRIES、22nm FD-SOIプロセスでの製造を2016年に開始か

GLOBALFOUNDRIES、22nm FD-SOIプロセスでの製造を2016年に開始か

GLOBALFOUNDRIESは、22nm FD-SOI(完全空乏型シリコン・オン・インシュレータ)プロセスの導入について、2016年末の量産開始を目指すという。同社は「28nm FinFETと同程度のコストで、14nm FinFETと同等の性能を実現できる」としている。 使い始めるとSSDの性能は低下する(前編)

使い始めるとSSDの性能は低下する(前編)

NANDフラッシュメモリを内蔵する全てのSSDに共通の特性として、SSDは使い始めると必ず性能が低下する。今回は、性能低下が起こる過程を見ていきたい。