SRAM同様、自由に配置できる混載フラッシュ:マスク4枚を追加するだけの低コスト製造対応(1/4 ページ)

不揮発メモリIPを手掛ける国内ベンチャー企業が、LSIのどこにでも配置できる新たな混載フラッシュメモリ技術を開発した。通常のCMOSプロセスに3〜4枚のマスクを追加するだけで実現できるといい、2016年中の量産対応を目指す。

産革機構も出資

システムLSIの設計が大きく変わるかもしれない。

不揮発性メモリIPを手掛ける新興企業 フローディアは、システムLSIの任意の位置に配置できる混載フラッシュメモリ技術「LEE Flash-G2」を開発した。2016年末にも同技術を用いた90nmプロセスによるシステムLSIの量産が始まる見込み。順次、55nmプロセスなどファウンドリ各社の微細プロセスへの対応を進め、LSI設計者にとって使いやすい不揮発性メモリとして幅広い普及を狙う。

プログラムやログ情報などのデータ格納用メモリとして、システムLSIへのフラッシュメモリの混載は増えている。マイコンなどでは、当たり前の存在だ。しかし、フラッシュメモリの混載は、LSI設計者には厄介な存在であり、フラッシュ混載が可能なプロセス世代を使用するカスタムLSIなどでもフラッシュを積まないことが多い。

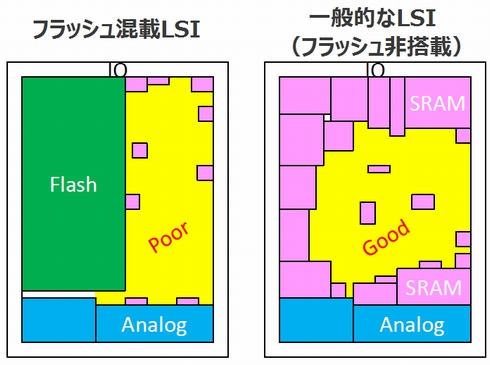

上に示した図の左側は、一般的なフラッシュメモリを混載したLSIのレイアウトだ。フラッシュメモリは、1カ所に集められ、かつ、チップの大部分を占める。一方で同じメモリのSRAM(図中のピンクの領域)は、ロジック回路(図中、黄色の領域)に接する形で点在している。

ロジックに寄り添えないフラッシュ

このような配置になる理由は、フラッシュメモリの駆動電圧の違いに起因する。ロジック部のCMOSプロセスよりも、高い駆動電圧を必要とするためであり、CMOSプロセスで構成できるSRAMのように、ロジックに寄り添えないのだ。

ロジックに寄り添えないが故に、フラッシュメモリの容量は気軽に増やすことができない。あらかじめ、必要と思われる容量分のスペースをフラッシュに割き、残された狭いスペースでロジック回路を配置していかなければならない。SRAMのように、必要な時に、必要な分だけ、ロジック近くに配置するというフレキシビリティがない。もっと言えば、フラッシュメモリは、混載といえど、実質的には、同一チップ上に載っているだけの別デバイスというような存在だ。加えて、ロジックやSRAM用のマスク以外に、フラッシュ用のマスクの追加が不可欠であり製造コスト増も招く。だから、システムLSI設計者にとっては、混載フラッシュは、邪魔な存在でしかないのだ。

この“邪魔な混載フラッシュ”を“身近で使いやすいフラッシュ”に変えることを狙ったのが、LEE Flash-G2だ。ロジックと寄り添えない高圧駆動を極力排除した独自の混載フラッシュメモリ構造を実現した。

Copyright © ITmedia, Inc. All Rights Reserved.