SRAM同様、自由に配置できる混載フラッシュ:マスク4枚を追加するだけの低コスト製造対応(4/4 ページ)

不揮発メモリIPを手掛ける国内ベンチャー企業が、LSIのどこにでも配置できる新たな混載フラッシュメモリ技術を開発した。通常のCMOSプロセスに3〜4枚のマスクを追加するだけで実現できるといい、2016年中の量産対応を目指す。

車載用途などで実績

フローディアは、2011年に、ルネサス エレクトロニクスでメモリ開発に従事した経歴を持つエンジニアが中心となって設立した混載不揮発メモリ専門のIPベンダー。同社のメモリIPの開発コンセプトは、低価格(Low Cost)、簡単(Easily)、混載可能(Embedded)の3つ。ホットエレクトロン注入方式よりも低電力動作可能でテストを簡素化できるFNトンネル注入技術と、シンプルな構造にできるSONOS型チャージトラップ技術をコア技術として、低コストで混載できるIPを開発してきた。

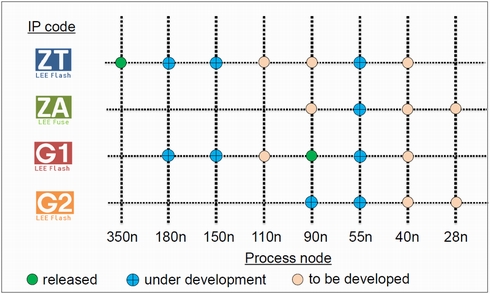

これまでに、メモリ専用の追加マスクゼロでフラッシュメモリを混載できる「LEE Flash-ZT」や、3枚程度のマスク追加で、高圧MOS版FNトンネル注入型SONOSフラッシュを構築できる「LEE Flash-G1」などのIPをリリース。同ZTは、国内外のファウンドリが対応する0.35μmプロセス版が、同G1も台湾Powerchipの90nmプロセス対応版がリリースされ、車載用を含むさまざまなLSIで採用されているという。

40nm、28nmへの対応も間もなく着手へ

開発した同G2についても、まず、実績あるPowerchipの90nmプロセスでの評価を先行させ、2016年末には同IPを用いたデバイスの量産が行える環境構築をめざす方針。その後、55nmプロセスや他のファウンドリへの展開を進めていく方針。同社会長を務める長沢幸一氏は「同G2は、現状10nm程度まで微細化することが可能であり、40nm、28nmプロセス対応に向けた開発も近く、着手する予定。設計者がフレキシブルに使えるフラッシュであり、LSI設計者に同G2の良さを理解してもらい、結果的に、対応ファウンドリを増やしていければと考えている」という。

なお、フローディアは2015年6月に、産業革新機構をはじめ三菱UFJキャピタル、大和企業投資から最大8億円の出資を得ることが決定。2021年に年間20億円以上を売り上げ、株式公開を目指している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

NANDフラッシュの基本動作(前編)

NANDフラッシュの基本動作(前編)

SSDを知るには、その記憶媒体として採用されているNANDフラッシュメモリを理解することも重要だ。今回は、NANDフラッシュメモリの基本動作を詳しく説明する。 メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目

メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目

今回は、大容量化と高速化が進む半導体メモリに焦点を当てる。メモリ市場の二大勢力となっているDRAMとNANDフラッシュメモリについての講演が多い。15nmプロセスを採用したNANDフラッシュメモリや、車載マイコン向けフラッシュメモリ技術、次世代のDRAMインタフェースなどに関する発表がある。 ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発

ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発

ルネサス エレクトロニクスは2015年2月25日、28nmプロセス世代の車載マイコン向けに、高速読み出し、高速書き換えを実現する新たな混載フラッシュメモリ技術を開発したと発表した。 65nmフラッシュ−ロジック混載プロセス、IoT機器向けマイコンなどに適用

65nmフラッシュ−ロジック混載プロセス、IoT機器向けマイコンなどに適用

東芝は、65nmロジックプロセスをベースにフラッシュメモリとロジック回路を混載できるプロセス「65nm−フラッシュ」を開発した。IoT(モノのインターネット)機器向けマイコンなどに適用していく。130nmのロジックプロセスとアナログパワープロセスをベースとした混載プロセス「130nm−NVM」も開発した。