SRAM同様、自由に配置できる混載フラッシュ:マスク4枚を追加するだけの低コスト製造対応(3/4 ページ)

不揮発メモリIPを手掛ける国内ベンチャー企業が、LSIのどこにでも配置できる新たな混載フラッシュメモリ技術を開発した。通常のCMOSプロセスに3〜4枚のマスクを追加するだけで実現できるといい、2016年中の量産対応を目指す。

サイズは1/3に

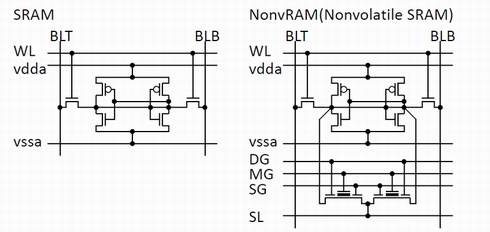

メモリセルから非コア電圧動作の高圧MOSを排除したこの「1トランジスタ3ゲート構造」により、多くの利点が生まれる。ソース/ドレインをコア電圧動作のスタンダードMOSで構成できるため、読み出し速度が高速化できる。また、従来、高圧を掛けるために、広げる必要のあったソースードレイン間、隣接するメモリセル間の間隔を狭められる。従来のFNトンネル方式のSONOS型チャージトラップフラッシュのセルサイズが70F2だったものが、LEE Flash-G2では18〜24F2となり、メモリ全体の面積も3分の1程度に小型化できるとする。

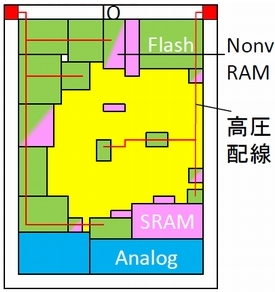

そして、唯一、高圧MOSが必要な、メモリゲートに印加する高圧電源部を分離、集中管理すれば、メモリセル自体は、ロジックに隣接して配置することが可能になる。すなわち、設計者は、フラッシュメモリがほしいところに、配置できるようになるのだ。

「SRAMに限りなく、似た構造であり、長く蓄積されてきたSRAMの設計技術が応用できる。面積次第だが、高速化するということも設計者側で選択できるようになる。フラッシュを混載するための、特殊なスキルは全く必要ない」(同社社長 奥山幸祐氏)という。

現実的な不揮発RAM

当然ながら、ロジックだけでなく、コア電圧で動作するSRAMとも隣接配置できる。このことは、SRAMとフラッシュメモリを組み合わせた“不揮発性RAM”が実現できることを意味する。「MRAMなど新素材を用いた不揮発性RAMの開発が進められているが、SRAMとLEE Flash-G2の不揮発RAMは、既存技術で構築でき、より現実的な解だと考えている」(奥山氏)とする。

従来のFNトンネル方式のSONOS型チャージトラップフラッシュよりもメモリセル構造は複雑になるが、「従来の1ゲート1トランジスタ構造の同メモリに、1枚マスクを追加するだけで、3ゲート1トランジスタ構造にできる。通常のCMOSプロセスに対してのマスク追加数は3〜4枚だけ」(奥山氏)とする。

Copyright © ITmedia, Inc. All Rights Reserved.