次々世代のトランジスタを狙う非シリコン材料(4)〜CMOSの実現手法と試作例:福田昭のデバイス通信(36)(2/3 ページ)

本シリーズは、次々世代のMOSFETで非シリコン材料がチャンネル材料の候補になっていることを説明してきた。最終回は、本シリーズのまとめであるCMOSデバイスの実現手法と試作例を紹介する。従来と同様のCMOSデバイスを非シリコン材料で実現する手法は2つある。

n型InGaAsとp型SiGeのCMOSリング発振器が動作

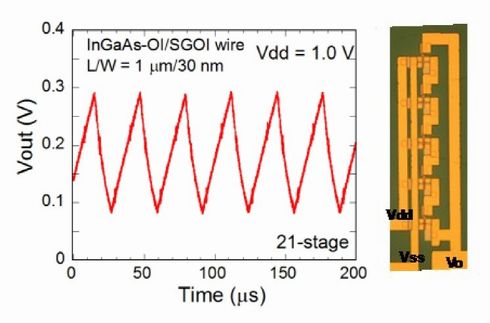

n型FETにInGaAsチャンネル、p型FETにGeチャンネルを採用するCMOSデバイスの研究では、簡単なICを試作して動作速度を測定する成果が出ている。2014年6月に国際会議VLSIシンポジウムで、産業技術総合研究所(産総研)がCMOSリング発振器を試作したと発表した。

産総研が試作したのは、21段のCMOSリング発振器である。電源電圧が1.0Vのときに、遅延時間が約35μs/段の速度で動作した。それほど高速であるとは言えないが、初期試作の段階であることを考慮すると、良好な値だとも言える。

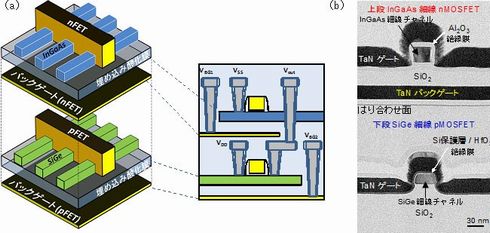

CMOS構造の作成方法は以下の通り。SiGe FETをSiウエハー上に形成した後で、InGaAs層を成膜済みのInPウエハーをSiウエハーにフェース・ツー・フェースで貼り合わせる。続いてInP層を取り除く。それからInGaAs FETを形成する。こうすると、p型SiGe MOS FETの上に、n型InGaAs MOS FETを積層したCMOS構造が出来上がる。

なお産総研は、上記の手法でp型Ge MOSFETの上にn型InGaAs MOSFETを積層したCMOSインバータ論理ゲートを試作し、2013年6月に国際学会VLSIシンポジウムでその概要を発表している。この発表が、InGaAs FETとGe FETのCMOSデバイスを初めて製造した研究成果である。

Copyright © ITmedia, Inc. All Rights Reserved.