次々世代のトランジスタを狙う非シリコン材料(4)〜CMOSの実現手法と試作例:福田昭のデバイス通信(36)(3/3 ページ)

本シリーズは、次々世代のMOSFETで非シリコン材料がチャンネル材料の候補になっていることを説明してきた。最終回は、本シリーズのまとめであるCMOSデバイスの実現手法と試作例を紹介する。従来と同様のCMOSデバイスを非シリコン材料で実現する手法は2つある。

Si基板からInGaAs層を横方向にエピタキシャル成長

SiウエハーとInPウエハーを貼り合わせる手法には、高価なInPウエハーを使用するので製造コストが上昇するという弱点がある。できれば、Siウエハーだけでn型InGaAs FETとp型Ge FET(あるいはp型SiGe FET)のCMOSデバイスを製造することが望ましい。

ここで課題となるのは、Siウエハーに高品質のInGaAs層を形成することである。Si表面に結晶成長したのでは、格子不整合によって欠陥だらけのInGaAs層ができてしまう。また絶縁層(酸化膜)表面に成膜したのでは、良好な品質のInGaAs層を得づらい。

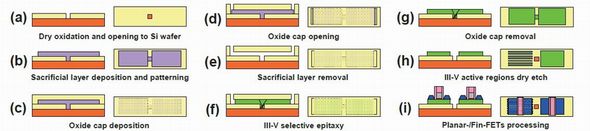

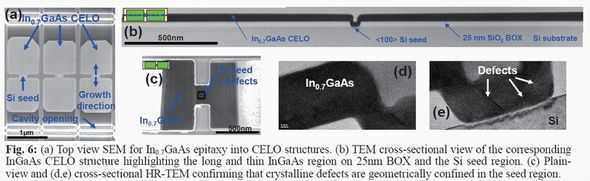

このような問題を解決する手法をIBMらの共同研究グループが開発し、2015年6月に国際学会VLSIシンポジウムで発表した。Siウエハー(Si基板)上に形成した絶縁層の「型(かた)」を埋めるように高品質のInGaAs層を横方向エピタキシャル成長させた。このエピタキシャル層を利用して、n型InGaAs MOSFETを試作してみせた。

試作したInGaAs MOSFETはトランジスタとして動作した。オン電流とオフ電流の比率は10の4乗で、まだ改良の余地があるものの、Si基板から直接成長させたInGaAs層としては非常に優れた値だと言える。トランジスタの性能指標である相互コンダクタンス(Gm)の最大値(ピーク値)は600μS/μm(ゲート長100nm)とこれも、かなり良好な値を得た。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

IBMがIII-V族化合物半導体を使ったFinFETの開発成果を積極的に発表している。IBMは、局所横方向エピタキシャル成長(CELO)技術により、シリコンおよびSOI基板の両方に、通常のCMOSプロセスで、InGaAsのFinFETを形成したと発表した。 ARMから見た7nm CMOS時代のCPU設計(18)〜壁に突き当たるリソグラフィ技術

ARMから見た7nm CMOS時代のCPU設計(18)〜壁に突き当たるリソグラフィ技術

プロセスルールの微細化において最も困難な課題は、リソグラフィ技術にある。7nm世代の半導体を量産するためのリソグラフィ技術は、いまだに確定していない。現在のところ、解決策としては、従来のArF液浸リソグラフィ技術の改善か、EUV(極端紫外光)リソグラフィ技術の開発が挙げられている。 CMOSイメージセンサーが引っ張る3次元積層技術

CMOSイメージセンサーが引っ張る3次元積層技術

チップを積層し、TSV(シリコン貫通電極)などで接続する3次元IC技術。CMOSイメージセンサーでも、3次元化が進んでいる。 ARMから見た7nm CMOS時代のCPU設計(13)〜高移動度FinFETの期待と現実

ARMから見た7nm CMOS時代のCPU設計(13)〜高移動度FinFETの期待と現実

FinFETの“延命策”として、チャンネルの材料をシリコンからゲルマニウム(Ge)やインジウム・ガリウム・ヒ素(InGaAs)などに変更する方法がある。だが、ARMの講演では、この“延命策”に悲観的だった。今回は、Ge FETなどが抱える問題と、その打開策について紹介する。