ナノインプリント開発の進展状況をキヤノンが講演(5)〜インプリント装置の開発ロードマップ:SEMICON West 2015リポート(12)(2/3 ページ)

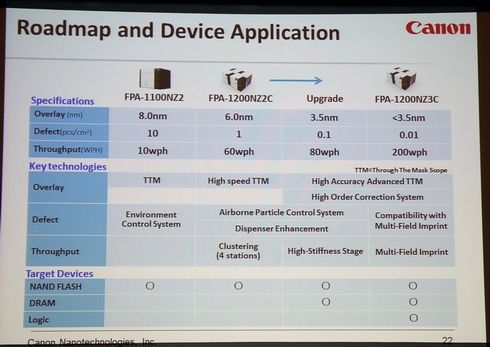

今回は、ナノインプリント・リソグラフィ技術の開発ロードマップを紹介しよう。キヤノンは現在、インプリント装置の第1世代機の開発を終えたところで、今後5年間で第2および第3世代機の開発に取り組んでいく予定だ。インプリント装置のターゲットは、NAND型フラッシュメモリとDRAM、ロジックICである。

ターゲットはNANDフラッシュとDRAM、ロジック

インプリント装置の世代交代から見ると、第1世代(初代)の装置「FPA-1100NZ2」の開発が完了したところである。次に第2世代機「FPA-1200NZ2C」を2016年内に開発する。そして第2世代機の性能を2017年〜2018年にアップグレードする。そして第3世代機「FPA-1200NZ3C」を2019年〜2020年に開発する、という計画である。

第1世代機「FPA-1100NZ2」は、半導体メーカーの生産ラインでプロセス開発に利用できる初めての本格的なインプリント・リソグラフィ装置である。スループットは10枚/時間、重ね合わせ誤差は8.0nm、欠陥密度は1cm2当たり10個という基本性能を備える。ターゲットの半導体デバイスはNANDフラッシュメモリである。

第2世代機「FPA-1200NZ2C」は初めてのクラスタ構成機である。4台のインプリント装置が連携して動く。全体のスループットは60枚/時間、装置1台当たりのスループットは15枚/時間に上昇する。その他の基本性能も重ね合わせ誤差は6.0nm、欠陥密度は1個/cm2と改良される。ターゲットの半導体デバイスは第1世代機と同様に、NANDフラッシュメモリである。

第2世代機を改良したアップグレード機はクラスタ構成を維持しながら、基本性能を向上させる。スループットが80枚/時間(全体)、重ね合わせ誤差が3.5nm、欠陥密度が0.1個/cm2というのが開発目標値である。ターゲットの半導体デバイスにはNANDフラッシュメモリの他に、DRAMが加わる。

そして第3世代機「FPA-1200NZ3C」では、本格的な量産に対応したスループット値である200枚/時間を装置4台のクラスタ構成で達成する計画である。その他の基本性能(目標値)は、重ね合わせ誤差が3.5nm未満、欠陥密度が0.01個/cm2となっている。ターゲットの半導体デバイスにはNANDフラッシュメモリとDRAMの他に、ロジックが加わる。

Copyright © ITmedia, Inc. All Rights Reserved.