連載

ナノインプリント開発の進展状況をキヤノンが講演(5)〜インプリント装置の開発ロードマップ:SEMICON West 2015リポート(12)(3/3 ページ)

今回は、ナノインプリント・リソグラフィ技術の開発ロードマップを紹介しよう。キヤノンは現在、インプリント装置の第1世代機の開発を終えたところで、今後5年間で第2および第3世代機の開発に取り組んでいく予定だ。インプリント装置のターゲットは、NAND型フラッシュメモリとDRAM、ロジックICである。

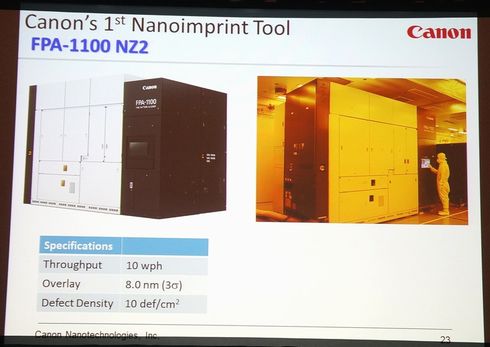

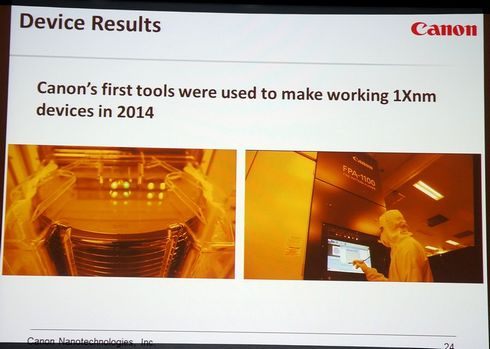

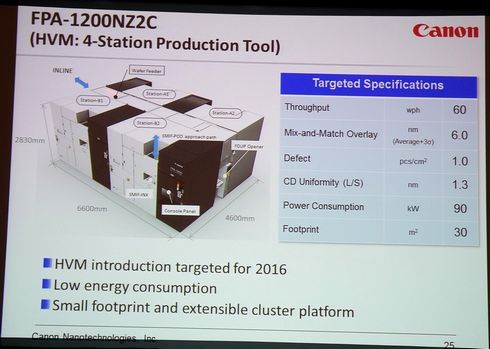

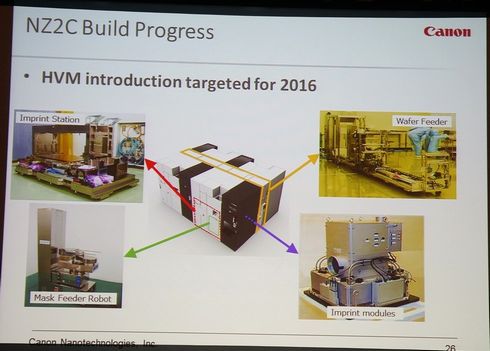

第1世代機「FPA-1100NZ2」と第2世代機「FPA-1200NZ2C」

講演者のResnick氏は、第1世代機「FPA-1100NZ2」が実際の半導体リソグラフィ工程で稼働している様子と、第2世代機「FPA-1200NZ2C」の概要を示した。第1世代機「FPA-1100NZ2」はNANDフラッシュメモリへの適用を想定してテストを重ねている。第2世代機「FPA-1200NZ2C」は、クラスタ構成の装置を組み立てているところだという。

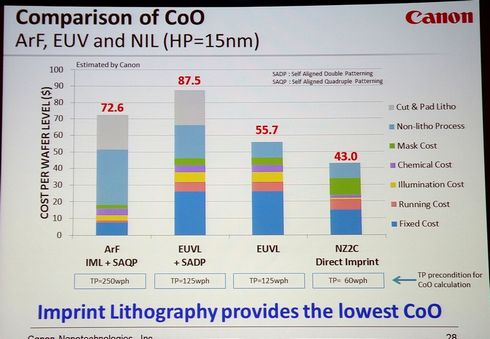

またハーフピッチ15nmを解像したときの、製造コストを比較してみせた。比較したのはナノインプリント技術とArF液浸SAQP技術、EUVリソグラフィとArF液浸SADPの混在技術、EUVリソグラフィ技術である。製造コストが最も低いのがナノインプリント技術、製造コストが最も高いのが、EUVリソグラフィとArF液浸SADPの混在技術となっていた。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ナノインプリント開発の進展状況をキヤノンが講演(3)〜生産性と欠陥密度

ナノインプリント開発の進展状況をキヤノンが講演(3)〜生産性と欠陥密度

ナノインプリント・リソグラフィでは、ウエハー1枚当たりの処理時間を短縮しようとすると、欠陥密度が増加する傾向にある。だが要求されるのは、生産性の向上と欠陥密度の低減だ。キヤノンは、こうした“二律背反”の要求に応えるべく、リソグラフィ技術の改良を重ねてきた。 ニコンが展望する10nm以下のリソグラフィ技術(前編)

ニコンが展望する10nm以下のリソグラフィ技術(前編)

本稿では、リソグラフィ技術の将来を14nm世代から5nm世代まで展望するシンポジウムにおける、ニコンの講演内容を紹介する。同社は、10nm世代にArF液浸露光技術を適用する場合、2つの大きな課題があると指摘した。「EPE(Edge Placement Error)」と「コストの急増」だ。 解像度10nm台の微細加工に対応可能、キヤノンのナノインプリント半導体製造装置

解像度10nm台の微細加工に対応可能、キヤノンのナノインプリント半導体製造装置

キヤノンは、開発中のナノインプリント技術を用いた半導体製造装置について、2015年中の製品化を目指している。同装置は解像度10nm台の微細加工に対応することが可能である。まずはフラッシュメモリの製造ラインへの導入を予定している。 20nm対応ナノインプリント用テンプレートの年内量産を発表――大日本印刷

20nm対応ナノインプリント用テンプレートの年内量産を発表――大日本印刷

大日本印刷(以下、DNP)は2015年2月19日、20nmレベルの半導体製造プロセスに対応したナノインプリントリソグラフィ(以下、NIL)用のテンプレート(型)の生産体制を構築し2015年にも量産を開始すると発表した。