PEZYのHPC用プロセッサ、64ビットMIPSコアを集積:1チップ当たり倍精度演算性能は8T FLOPS(1/2 ページ)

イマジネーション・テクノロジーズとPEZY Computingは、次世代HPC(High Performance Computing)システム開発に向けて提携した。PEZYが開発中の次世代メニーコアプロセッサに、イマジネーションの64ビットMIPSプロセッサコアをオンチップで搭載する。

ImaginationとPEZY Computingが提携

Imagination Technologies(イマジネーション・テクノロジーズ)とPEZY Computing(以下、PEZY)は2015年11月16日、次世代HPC(High Performance Computing)システム開発に向けて提携したと発表した。PEZYが開発中の次世代メニーコアプロセッサに、イマジネーションの64ビットMIPSプロセッサコアをオンチップで搭載するなどして、1チップ当たりの倍精度演算性能を8T(テラ)FLOPSに高める。

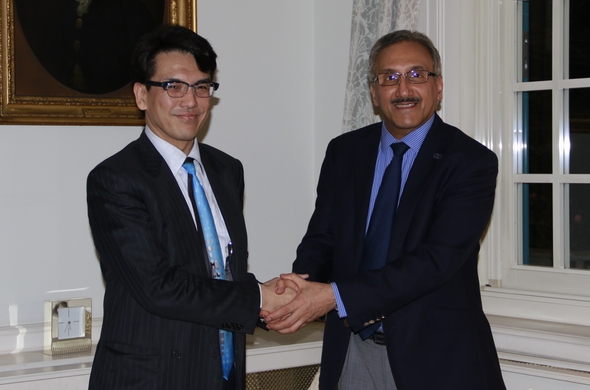

イマジネーション・テクノロジーズとPEZY Computingが提携。左はPEZYの社長を務める齊藤元章氏、右はImagination TechnologiesのCEOを務めるHossein Yassaie氏

PEZYは、MIMD(Multiple Instruction,Multiple Data)型の大規模メニーコアプロセッサの開発を目的として、2010年に設立されたベンチャー企業である。経済産業省や新エネルギー・産業技術総合開発機構(NEDO)の支援を受けて、これまでメニーコアプロセッサとして、演算素子(PE:Processor Element)が512コアの「PEZY-1」や、同1024コアの「PEZY-SC」を開発してきた。PEZY-SCは、高エネルギー加速器研究機構(KEK)に設置された「Suiren(睡蓮)」などのアクセラレータとして実装されている。

現在は、2016年末のES出荷に向けて、PE数を現行製品の4倍となる4096コアに増やした第3世代の「PEZY-SC2」を開発中である。この中に、汎用演算用途でイマジネーションの64ビットMIPSプロセッサコア「Warrior CPU」を、複数個オンチップで搭載することに決めた。

Warrior CPUを選択した理由について齊藤氏は、「PEZY-SC2の仕様はまだ流動的である。こうした中でイマジネーションからは、搭載するCPUコア数やその種類、チップの構成などについて選択のオプションを与えてもらえるなど、柔軟性があった。技術サポートについても、強力なコミットメントが得られた」と述べた。

これまでのPEZY-SCにも、ARM926コアを2個内蔵しているが、主に管理/デバッグ用として用いている。複雑な処理などを行う場合は、外部に接続されたIntel製のホストCPU「Xeon」で実行していた。しかし、演算性能をさらに高め、消費電力を抑えようとすると、PCIeなどを介したチップ間の通信速度がシステム性能を向上するうえでボトルネックになりかねない。そこで、汎用CPUコアもオンチップで集積することにした。

Copyright © ITmedia, Inc. All Rights Reserved.