拝幚側恑揥傪尒偣傞MRAM媄弍丗暉揷徍偺僨僶僀僗捠怣 IEDM 2015僾儗價儏乕乮10乯乮1/2 儁乕僕乯

崱夞偐傜丄僇儞僼傽儗儞僗嵟廔擔偺僙僢僔儑儞傪徯夘偡傞丅僙僢僔儑儞26偼丄乽MRAM丄DRAM偲SRAM乿傪僥乕儅偵島墘偑恑傫偱偄偔丅MRAM偵偮偄偰偼寁4審偺榑暥敪昞偑偁傝丄椺偊偽Qualcomm Technologies傜偼丄40nm儖乕儖偺CMOS儘僕僢僋偵杽傔崬傓偙偲傪憐掕偟偨STT-MRAM媄弍傪曬崘偡傞丅

儔僗僩儗儀儖偺僉儍僢僔儏偵MRAM傪棙梡

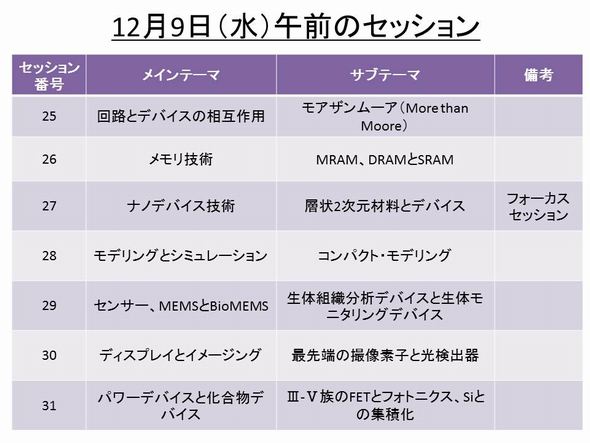

丂2015擭12寧偵奐嵜梊掕偺崙嵺妛夛乽IEDM 2015乿偐傜丄僇儞僼傽儗儞僗3擔栚乮嵟廔擔乯偱偁傞12寧9擔乮悈乯偺屵慜偵梊掕偝傟偰偄傞堦斒島墘僙僢僔儑儞傪夝愢偡傞丅9擔屵慜偺帪娫懷偵偼丄僙僢僔儑儞25偐傜僙僢僔儑儞31傑偱偺7杮偺僙僢僔儑儞偑摨帪暲峴偵恑傓丅

丂崱夞偼僙僢僔儑儞25乮夞楬偲僨僶僀僗偺憡屳嶌梡乯偲僙僢僔儑儞26乮儊儌儕媄弍乯偺2偮偺僙僢僔儑儞偵偮偄偰丄奣梫傪愢柧偟傛偆丅

丂僙僢僔儑儞25乮夞楬偲僨僶僀僗偺憡屳嶌梡乯偺僒僽僥乕儅偼丄乽儌傾僓儞儉乕傾乮More Than Moore乯乿偱偁傞丅偙偺僙僢僔儑儞偱偼廬棃偺僔儕僐儞MOSFET偲偼丄彮偟堘偭偨傾僾儘乕僠偵傛傞尋媶惉壥偑斺業偝傟傞丅

丂搶幣偼丄帴婥僩儞僱儖愙崌乮MTJ乯慺巕傪儊儌儕僙儖偵棙梡偟偨掅徚旓丒掅僐僗僩偺僆儞僠僢僾僉儍僢僔儏媄弍傪曬崘偡傞乮島墘斣崋25.1乯丅MTJ慺巕傪巊偭偨帴婥儊儌儕乮MRAM乯偼丄廬棃偺僆儞僠僢僾僉儍僢僔儏媄弍偱偁傞SRAM偵斾傋傞偲懍搙偱偼楎傞傕偺偺丄晄婗敪惈儊儌儕側偺偱徚旓揹椡偑掅偄丄婰壇梕検摉偨傝偺僔儕僐儞柺愊偑彫偝偄乮惢憿僐僗僩偑掅偄乯偲偄偭偨摿挿偑偁傞丅偦偙偱搶幣偱偼丄MTJ慺巕傪巊偭偨儊儌儕傪CPU偺僆儞僠僢僾2師僉儍僢僔儏偲3師僉儍僢僔儏乮偁傞偄偼儔僗僩儗儀儖僉儍僢僔儏乯偵墳梡偡傋偔丄尋媶奐敪傪懕偗偰偒偨丅IEDM 2015偱偼丄2師僉儍僢僔儏偵2T乮僩儔儞僕僗僞乯2MTJ僙儖丄3師僉儍僢僔儏偵1T1MTJ僙儖傪嵦梡偟偨僉儍僢僔儏媄弍傪敪昞偡傞丅婛懚偺SRAM僉儍僢僔儏媄弍偵斾傋丄CPU偺徚旓揹椡傪65亾丄僔儕僐儞僟僀柺愊傪37亾偵掅尭偱偒偨偲偄偆丅

丂TSMC偼丄儈儕攇庴摦慺巕孮傪1屄偺僂僄僴乕丒儗儀儖丒僷僢働乕僕偵廤愊偡傞媄弍傪奐敪偟偨乮島墘斣崋25.2乯丅僀儞僟僋僞丄儕儞僌嫟怳婍丄揹椡崌惉婍丄寢崌婍丄僶儔儞丄揱憲慄楬丄傾儞僥僫側偳傪傑偲傔偨丅掅嶨壒偱掅徚旓揹椡偺儈儕攇僔僗僥儉傪儌僶僀儖抂枛傗IoT抂枛側偳偵岦偗偰幚尰偱偒傞丅

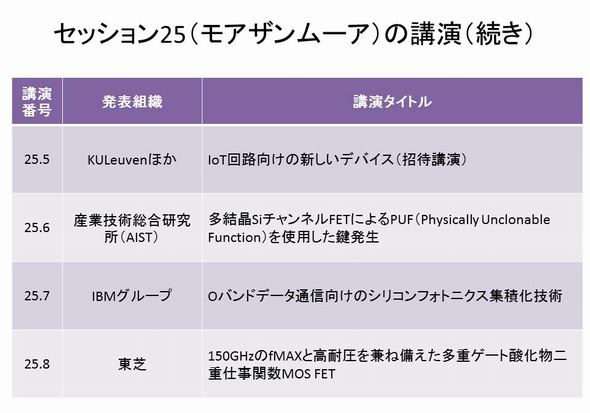

丂IBM Microelectronics偲IBM Research偺嫟摨尋媶僠乕儉偼丄O僶儞僪乮攇挿1.26兪m乣1.36兪m丄廃攇悢220THz乣238THz乯傪棙梡偟偨岝僨乕僞捠怣偵岦偗偨僔儕僐儞丒僼僅僩僯僋僗媄弍傪敪昞偡傞乮島墘斣崋25.7乯丅CMOS媄弍偲RF媄弍丄岝僄儗僋僩儘僯僢僋僨僶僀僗偱峔惉偟偨丅僠儍儞僱儖摉偨傝25G價僢僩/昩偺岝儕儞僋傪4僠儍儞僱儖梡堄偟偨丅岝僼傽僀僶乕偲偼帺屓惍崌偱愙懕偡傞丅

Copyright © ITmedia, Inc. All Rights Reserved.