スピン論理で低消費・高密度の回路を構築:福田昭のデバイス通信 IEDM 2015プレビュー(13)(2/3 ページ)

13回にわたりお届けしてきたIEDM 2015のプレビューは、今回が最終回となる。本稿ではセッション32〜35を紹介する。折り曲げられるトランジスタや、電子のスピンを利用した論理回路、疾患を素早く検知する人工知能ナノアレイ技術などに関連する研究成果が発表される。

疾患を迅速に検出する揮発性有機物の分析技術

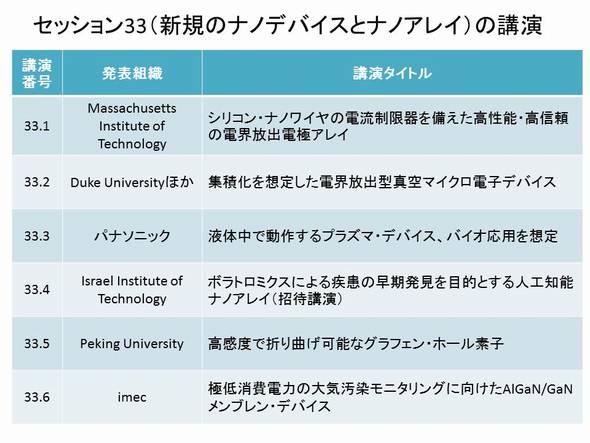

セッション33(センサー、MEMSとBioMEMS)のサブテーマは「新規のナノデバイスとナノアレイ」である。電界放出を利用したデバイスやバイオ応用を狙ったデバイスなどの研究成果が発表される。

Massachusetts Institute of Technologyは、電流密度が平方センチ当たりで100Aを超えるシリコン電界放出電極アレイを発表する(講演番号33.1)。動作電圧は60Vで、電界放出デバイスとしては低いとする。シリコンのナノワイヤによる電流制限器を放出電極ごとに設けたことで、電流の調整を容易にした。

Israel Institute of Technologyは、呼気や皮膚、尿、血液などに含まれる揮発性有機化合物を分析することで、疾患を素早く検知する人工知能ナノアレイ技術を解説する(講演番号33.4)。特定の疾患が副産物として特定の揮発性有機化合物を発生する現象を利用する。この手法は「ボラトロミクス」と呼ばれ、安価で迅速な疾患診断の支援技術として期待がかかっているとする。

ナノワイヤFET材料の最適な組み合わせを求める

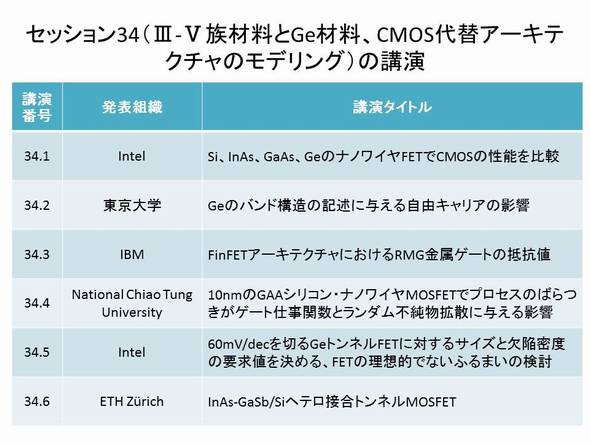

セッション34(モデリングとシミュレーション)のサブテーマは「III-V族材料とGe材料、CMOS代替アーキテクチャのモデリング」である。

Intelは、さまざまな材料でナノワイヤMOSFETのCMOS回路を構成したときの性能をシミュレーションで比較して見せる(講演番号34.1)。材料はSi、InAs、GaAsとGe、ゲート長は13nmである。歪みを考慮した原子論的量子輸送シミュレーションでベンチマーク値を求めた。GeのCMOSが駆動電流が最も高く、III-V族とGeのハイブリッドCMOSが消費電力が最も低くなる。

ETH Zurichは、InAs-GaSb二重ゲート極薄ボディとInAs-Siゲートオールアラウンド(GAA)・ナノワイヤ・トンネルMOSFETのデバイスを量子輸送シミュレーションで解析した結果を報告する(講演番号34.6)。ゲート長やボディの厚さ、ボディの大きさを変えて比較した。急峻なサブスレッショルド特性と高いオン電流を得るには、従来のトンネルFETよりもデバイスを厚くすべきとの指針をシミュレーションは示唆しているという。

Copyright © ITmedia, Inc. All Rights Reserved.