産総研、TMR素子の記憶安定性を約2倍に向上:大容量STT-MRAMの開発を加速

産業技術総合研究所(産総研)の薬師寺啓氏は、スピントルク書込型磁気ランダムアクセスメモリ(STT-MRAM)に用いられる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を従来の2倍に向上させることに成功した。素子サイズが20nm以下の大容量SST-MRAMを実現することが可能となる。

産業技術総合研究所(産総研)スピントロニクス研究センター金属スピントロニクスチームの研究チーム長を務める薬師寺啓氏は2015年12月、スピントルク書込型磁気ランダムアクセスメモリ(STT-MRAM)に用いられる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を、従来の2倍に向上させることに成功したと発表した。素子サイズが20nm以下の大容量SST-MRAMを実現可能にする技術だという。

TMR素子は、次世代メモリとして注目を集めるSTT-MRAMを実現するためのコア技術となる。これまで産総研が東芝らと共同開発してきたTMR素子のサイズは、記憶安定性の点から30nmが限界となっていた。しかし、DRAMなどの代替メモリとして実用化するには、素子サイズを20nm以下にする必要がある。半面、素子サイズを小さくすると記憶安定性が悪くなるという課題もあった。

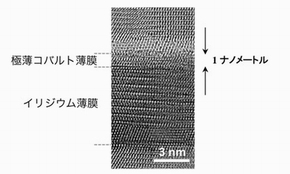

そこで産総研は、情報記憶を行う「記憶層」にイリジウム薄膜と極薄のコバルト薄膜を用いるなど、新たな構造や材料を採用することで高い記憶安定性を実現することに成功した。具体的には、イリジウム薄膜と極薄コバルト薄膜を素子の下部に形成し、その上部に各薄膜を積層した。イリジウム薄膜上に形成したコバルト薄膜の厚みはわずか1nmである。記憶層は、コバルト(Co)/タングステン(W)/鉄ボロン(Fe-B)と3層一体の構造となる。この記憶層がSTT-MRAMの1つのメモリとして機能する。

新開発の垂直磁化TMR素子は、新たな材料や構造を採用しつつ、従来と同等の低い素子抵抗(RA)値と高い磁気抵抗(MR)比を両立した。コバルト薄膜の上にタングステンを挿入することで、異方性エネルギーを従来に比べて約2倍に向上させることができた。この結果、記憶層の体積は同じだが記憶安定性は2倍となった。

こうした特性の改善により、19nmサイズのSTT-MRAMを実現することが可能となった。産総研では引き続き、より高い記憶安定性の実現に取り組むことにしており、大容量STT-MRAMの実用化開発に弾みをつける。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

産総研、軽元素を原子レベルで可視化

産総研、軽元素を原子レベルで可視化

産業技術総合研究所(産総研)ナノ材料研究部門の末永和知首席研究員と同部門で電子顕微鏡グループの千賀亮典研究員は、低加速電子顕微鏡を用いて、リチウムを含む軽元素を原子レベルで可視化することに成功した。 産総研など提案の「樹脂と金属接合特性評価試験方法」がISO規格に

産総研など提案の「樹脂と金属接合特性評価試験方法」がISO規格に

産業技術総合研究所と日本プラスチック工業連盟は、両者が開発した「樹脂と金属の接合界面の特性評価試験方法」が、国際規格「ISO19095シリーズ」として発行されることになったと発表した。 6インチウエハーによるSiCチップ試作ライン構築

6インチウエハーによるSiCチップ試作ライン構築

つくばイノベーションアリーナ(TIA)は、6インチ級SiC(炭化ケイ素)ウエハーを用いたパワー半導体デバイスの量産研究開発を目的に、新たな第3ラインを産業技術総合研究所(産総研)西事業所内に構築する。 印刷技術で、有機強誘電体メモリの3V動作を確認

印刷技術で、有機強誘電体メモリの3V動作を確認

産業技術総合研究所の野田祐樹氏らは、低電圧でも動作する有機強誘電体メモリの印刷製造技術を開発した。この技術を用いて作成した薄膜素子は、電圧3Vでメモリ動作することを確認した。