IEDMで発表されていた3D XPointの基本技術(前編):福田昭のデバイス通信(60)(1/2 ページ)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。

3D XPointの要素技術が一部明らかに

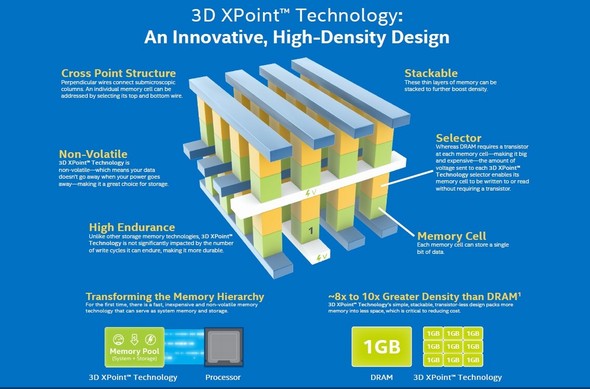

謎に包まれていた次世代メモリ技術「3D XPoint(スリーディー・クロスポイント)」の要素技術が一部、明らかになった。3D XPointメモリは、IntelとMicron Technologyが共同開発し、両社が2015年7月29日(米国時間)に大々的に発表した次世代の不揮発性メモリである*)。DRAMに比べて10倍も記憶密度が高く、NANDフラッシュメモリに比べて1000倍もアクセスが速く、NANDフラッシュメモリの1000倍の書き換え寿命を有すると喧伝(けんでん)された。

*)関連記事:IntelとMicronの新不揮発メモリ「3D XPoint」

華々しく発表されたにもかかわらず、3D XPointのメモリ技術は具体的な記述が避けられていた。分かっているのは、2層のクロスポイント・メモリであることと、記憶容量が128Gbitと大容量であること(つまり1層当たり64Gbitであること)くらい。次世代不揮発性メモリの研究開発コミュニティーでは、2層のクロスポイント構造は特に珍しくはない。さすがに128Gbitもの大容量チップを開発した事例は学会で公表されていないものの、2層のクロスポイント構造で32Gbitの大容量チップ(抵抗変化メモリ)はSanDiskと東芝が共同で試作し、国際学会ISSCCで2013年2月に発表済みである。

3D XPointメモリは報道機関向けの説明会や説明動画の公表などはなされたものの、2016年1月の時点では、技術内容が国際学会で発表された形跡は見当たらない。その実現技術はベールに包まれていた。

そんな中で、半導体製造装置と半導体材料の業界団体SEMIが2016年1月10日〜13日に米国カリフォルニア州のベイエリア(サンフランシスコとシリコンバレーの中間点)で開催した有償の業界イベントISS(Industry Strategy Symposium)で、1月12日にIntelとMicronの合弁によるNANDフラッシュメモリの開発製造企業IM Flash Technologiesが3D XPointメモリの要素技術を一部、明らかにした。発表者は同社の共同CEOをつとめるGuy Blalock氏である。Blalock氏の講演概要は、本誌が報告済みだ*)。

*)関連記事:3D XPoint、開発から製造へ

Blalock氏の講演で最も重要なポイントは、メモリセルの要素技術が示されたことだろう。本誌の既報によると「3D XPoint技術は、カルコゲナイド材料と『Ovonyx』のスイッチを使用している」とある。ここから、記憶素子はカルコゲナイド材料、セル選択素子はOvonic(オボニック)スイッチであることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.