IEDMで発表されていた3D XPointの基本技術(前編):福田昭のデバイス通信(60)(2/2 ページ)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。

1960年代に発見された「オブシンスキー効果」が源流

記憶素子がカルコゲナイド材料であることから、記憶原理は「相変化」だと推定する。3D XPointメモリは、相変化メモリの一種だと見なせる。

注目すべきは、セル選択素子が「オボニック・スイッチ」だということだ。オボニック・スイッチ、厳密には「オボニック・スレッショルド・スイッチ(OTS:Ovonic Threshold Switch)」と呼ばれるスイッチは、米国を代表する発明家Stanford R. Ovshinsky氏が1960年代に発見した、カルコゲナイド材料の重要な性質に基いている。「Ovshinsky(オブシンスキー)効果」とも呼ばれるこの現象は、カルコゲナイド材料が電気的性質と光学的性質の異なる状態を可逆的に行き来することで知られる。

オブシンスキー効果からは2つの電気素子が生まれた。1つが相変化メモリ(PCM:Phase Change Memory)、もう1つが超高速スイッチ(OTS)である。相変化メモリには光学的なメモリと電気的なメモリの両方が存在し、光学的なメモリは相変化型光ディスクとして商品化された。

3D XPointメモリは、セル選択素子と記憶素子の両方にカルコゲナイド材料を使い、動作原理はいずれも、オブシンスキー効果に基づく。Blalock氏の講演に「その開発に向けた取り組みの歴史は、1960年代にまでさかのぼる」とあるのは、1960年代に発見されたオブシンスキー効果と、この効果を利用した研究開発の長い歴史を指していると思われる。

2009年の国際学会IEDMで3D XPointメモリのひな型を公表

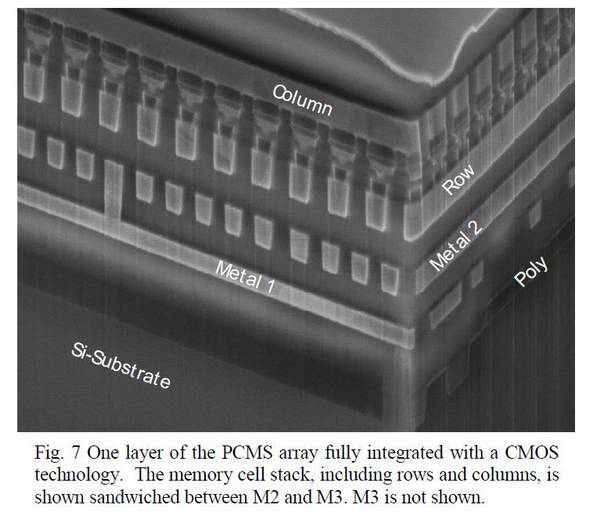

PCMとOTSを利用した3次元(3D)積層可能なクロスポイント・メモリは、電子デバイス技術の国際学会IEDMで発表されたことがある。IntelとNumonyxが共同で、2009年のIEDMで試作チップを公表していた(講演番号27.1)。Numonyxは、IntelとSTMicroelectronicsが合弁で設立したフラッシュメモリの開発企業であり、2010年にMicronによって買収された。IntelとNumonyxの組み合わせが、IntelとMicronの組み合わせに変わり、3D XPointメモリへと至る流れができたことになる。

IntelとNumonyxが2009年のIEDMで公表した試作チップは、90nmのCMOS技術によって製造された。記憶容量は64Mbit、クロスポイントの層数は1層である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「SSDが壊れる」まで(前編)

「SSDが壊れる」まで(前編)

ノートPCなどのストレージとして急速に市場が拡大しているSSD(Solid State Drive)。その信頼性に対するイメージはHDDと比較されることが多いが、「平均故障間隔」と「年間故障率」の数値を単純に比較すればいいというわけではない。そこで今回は、SSDの寿命にかかわる要素を解説する。 東芝、SSD並みの性能を実現する組み込みNANDメモリ用コントローラ開発

東芝、SSD並みの性能を実現する組み込みNANDメモリ用コントローラ開発

東芝は、組み込み式ストレージメモリ標準規格である「JEDEC Universal Flash UFS Version 2.0」などに準拠し、「世界最高速」(同社)というUFSメモリコントローラを開発した。従来コントローラに比べ、ランダムリード性能で約10倍の性能を達成したという。 2014年7〜9月のNANDフラッシュ市場シェア、東芝がサムスンとの差を縮める

2014年7〜9月のNANDフラッシュ市場シェア、東芝がサムスンとの差を縮める

2014年第3四半期のNAND型フラッシュメモリ市場は好調だ。前四半期比で最も成長したのは東芝で、売上高は23%増加している。一方、売上高でトップのSamsung Electronics(サムスン電子)は8%増で、シェアは3割を切った。 「3D XPoint」は相変化メモリか――特許から詮索

「3D XPoint」は相変化メモリか――特許から詮索

Intel(インテル)とMicron(マイクロン)がこのほど発表した不揮発性メモリ「3D XPoint」は本当に相変化メモリの1つなのか? 筆者が特許をウェブで検索したところ、この見方を裏付ける結果となった。