ルネサス 90nm BCDプロセス混載可能なフラッシュ:次世代車載マイコンに適用へ(1/3 ページ)

ルネサス エレクトロニクスは2016年2月3日、90nm世代のBCDプロセスに混載可能なフラッシュメモリ技術を開発したと発表した。豊富なアナログ/パワー回路を備えたBCDプロセス採用マイコンにフラッシュメモリを搭載できるようになる。

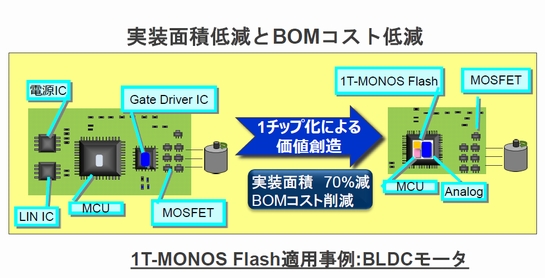

ルネサス エレクトロニクスは2016年2月3日、90nm世代のBCDプロセスに混載可能なフラッシュメモリ技術を開発したと発表した。豊富なアナログ/パワー回路を備えたBCDプロセス採用マイコンにフラッシュメモリを搭載できるようになり、同マイコンが使用されることの多い自動車のECU(電子制御ユニット)などの小型化、低コスト化が可能になる。

90nmBCDプロセスを2015年量産化済み

BCDプロセスとは、特徴の異なるBipolar(バイポーラ)プロセス、CMOSプロセス、DMOSプロセスの3種のプロセスを同時に実現する製造プロセスだ。一般的には、バイポーラは高精度のアナログ回路に、DMOSは数十ボルトクラスの高耐圧素子に、CMOSはロジック回路に向くとされる。BCDプロセスは、これらのプロセスを同時に実現できるため、従来はプロセスごとのチップ構成となった回路/素子を、1チップに集積できる。

こうした利点を持つBCDプロセスは、小型化/軽量化、低コスト化などが求められる車載向けデバイスに用いられるケースが増えている。マイコン、アナログ/パワー回路を搭載したデバイスであれば、自動車に多く搭載されるモーターの駆動から制御までを1チップで行えるからだ。

ルネサスは、「BiCDMOSプロセス」と呼ぶBCDプロセスを開発し、車載デバイス向けを中心に展開。2015年には、BCDプロセスとしては最も微細な90nm世代の技術を確立し、デバイスの量産出荷を開始している*)。

*)関連記事:ルネサス、車載向け90nm BCDプロセス量産を発表

BCDプロセスに混載できなかったフラッシュメモリ

3種のプロセスを同時実現するBCDプロセスだが、あらゆる回路/素子を集積できるわけではない。集積できない回路/素子の1つがフラッシュメモリだ。フラッシュメモリ内蔵マイコンなどCMOSプロセスでのフラッシュメモリの混載は確立されている。だが、BCDプロセスでは、アナログ/パワー部から発せられる熱などの影響で、十分な信頼性を確保できず混載が難しかった。またフラッシュメモリの混載は、多くの追加工程/マスクが必要であり、製造コストの観点からも困難だった。

そうした中で、ルネサスは、BCDプロセスに対応するフラッシュメモリ技術を開発し、2016年1月31日〜2月4日の会期で開催されている半導体集積回路技術国際会議「ISSCC 2016」で発表を行った。

1T-MONOSで

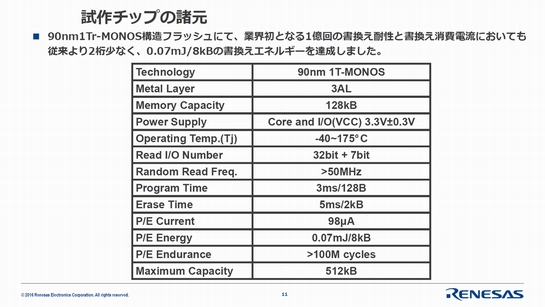

開発したフラッシュメモリは、追加工程が少なくて済む1トランジスタ(1Tr)タイプのMONOS*)構造のフラッシュメモリ。ジャンクション温度(Tj)175℃環境でも書き換え耐性1億回という高い信頼性を備える。

*)MONOS:Metal Oxide Nitride Oxide Siliconの略。

Copyright © ITmedia, Inc. All Rights Reserved.