キャッシュメモリの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(6)(2/3 ページ)

今回は、キャッシュメモリについて解説する。キャッシュの考え方はとてもシンプルだが、実装となるとさまざまな方法があって複雑だ。今回は、3つのキャッシュアクセス構造について説明しよう。

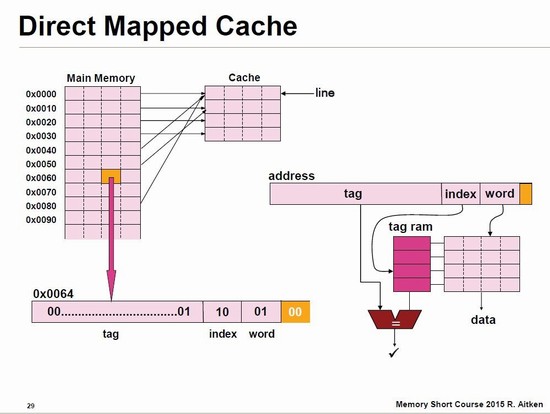

キャッシュアクセスの構造

キャッシュを備えたメモリ・システムでは、CPUがメモリにアクセス要求を出すと、アクセス要求に対応するアドレスがキャッシュに存在するか、主記憶(システム・メモリあるいはメインメモリ)に存在するかを、ハードウェアがすぐさま判断しなければならない。このキャッシュアクセスの構造(アーキテクチャ)には、いくつかの方法がある。

最も単純な方式は、CPUが要求したアドレスと、キャッシュのタグを全て比較するというものだ。例えば256本のラインがあったとすると、全てのラインのタグ(アドレス)、すなわち256個のアドレスと要求されたアドレスを照らし合わせる。この方式(構造)を「フルアソシアティブ方式」と呼ぶ。

この方式の利点は、キャッシュと主記憶のやりとりに制限がないことだ。どのアドレスのデータでも、主記憶から、全てのキャッシュラインにコピーが可能である。言い換えると、これから述べるフルアソシアティブ以外の方式(構造)では、キャッシュと主記憶のやりとりに何らかの制限が加わるということでもある。

フルアソシアティブ方式の欠点は、回路の規模が大きくなることと、その規模の大きな回路を極めて高速に動かさなければならないことだ。また消費電力が大きくなるという問題も抱える。このため、組み込みシステムのキャッシュではフルアソシアティブ方式はあまり使われない。

これに対して、主記憶のアドレスから、キャッシュラインの位置をあらかじめ決めてしまうのが、「ダイレクトマッピング方式」である。具体的には、メモリアドレスの一部(中位のアドレス)を、キャッシュラインのアドレスに割り当てる。この割り当てるアドレスを「インデックス」と呼ぶ。

ダイレクトマッピング方式の利点は、インデックスを利用してキャッシュのタグメモリ(SRAM)とデータメモリ(SRAM)を読みに行くという動作になるため、回路規模がコンパクトであり、回路の動作を高速にしやすいことだ。

もちろん欠点もある。最大の問題は、主記憶で同じインデックスに対応するデータは複数個存在するのに対し、キャッシュで格納可能なラインが1個しかないことだ。つまり、既にデータが埋まっているキャッシュラインには、同じインデックスのデータを格納するには前のデータを消して上書きするしか、方法がない。

Copyright © ITmedia, Inc. All Rights Reserved.